- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32U575: ADF1 does not work when selecting P...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32U575: ADF1 does not work when selecting PLL3Q for clock source

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-16 8:29 PM

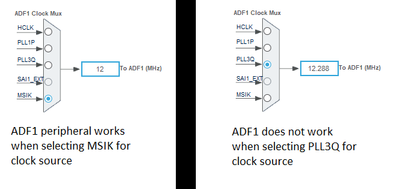

I’ve been working with the STM32U575RIT6 and it’s ADF1 peripheral. I have a digital MEMS microphone connected to the ADF1 pins on the micro. I’ve been following the “ADF_AudioRecorder” example provided with the STM32Cube firmware. I can get the code to work just fine when selecting the MSIK clock for the ADF1 peripheral, but the peripheral stops working when I select PLL3Q for the clock source. See the attached screenshots from CUBEMX.

PLL3Q clock is generated from an external crystal (HSE). I’ve verified that the crystal is working on my custom board.

Can someone help explain why I’m having this problem? Thanks!

- Labels:

-

STM32U5 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-17 1:54 AM

Hello @coppercrimp ,

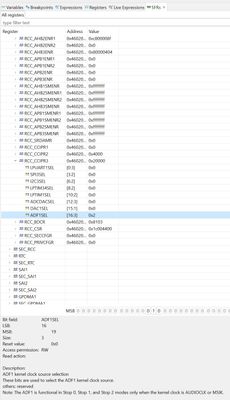

Could you confirm the same issue when using pll1_p_ck or AUDIOCLK or HCLK? A screenshot of RCC_CCIPR3 in debug would be helpful.

Do you enter a stop mode in your code?

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-17 7:31 PM

Hi F.Belaid, thank you for your help with this. As you suggested, I tried using PLL1P to clock the ADF1 peripheral and it works properly. I have not tried AUDIOCLK or HCLK yet, but so far PLL1P and MSIK clocks both work as expected. But PLL3Q still does not work. Both PLL1P and PLL3Q are sourced from and external 12.288MHz quartz crystal.

I used an oscilloscope to probe the ADF1_CCK0 pin (PB3) and no clock appears as an output on this pin when using PLL3Q. I can see a clock signal when using PLL1P or MSIK clock sources.

I've attached a screenshot of the RCC_CCIPR3 register when PLL3Q is selected as the clock source

One more thing - I do not enter stop mode anywhere in my code.

Thanks again, and best regards

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-20 7:37 AM

Hello @coppercrimp ,

Thank you for the feedback, I reproduced the issue. I suggest this workaround,

__HAL_RCC_PLLCLKOUT_ENABLE(RCC_PLL3CFGR_PLL3QEN);

instead of //ret = RCCEx_PLL3_Config(&(pPeriphClkInit->PLL3));

Hope this helps!

Firas

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-20 10:04 AM

Hi Firas,

Thank you for the suggestion, but unfortunately I'm still having the same issue. I replaced all occurrences of

ret = RCCEx_PLL3_Config(&(pPeriphClkInit->PLL3));with

__HAL_RCC_PLLCLKOUT_ENABLE(RCC_PLL3CFGR_PLL3QEN);in the file "stm32u5xx_hal_rcc_ex.c". After making the changes, the same problem I reported in my original post still persists. Do you have any other suggestions I might be able to try?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-21 4:29 AM

Hello Again @coppercrimp

Would you please share your IOC file? It is possible that there is something missing in the configuration of the external crystal (HSE)

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- lib_nfc support for NFC tag Type 4 in STM32 MCUs Embedded software

- STm32f407: Which Registers control HSI or HSE oscillator selection and PLL clock source? in STM32 MCUs Products

- WWDG on HSE not stopping when enter STOP mode. in STM32 MCUs Products

- Advice on STM32 MCU and Baremetal/FreeRTOS selection in STM32 MCUs Embedded software

- STM32U575xx - I2C slaves do not send ACK resulting in `HAL_I2C_ERROR_AF` error in STM32 MCUs Embedded software