STM32H745/755 clock setup with LL libs doesn't work properly (CubeMX)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 12:32 AM

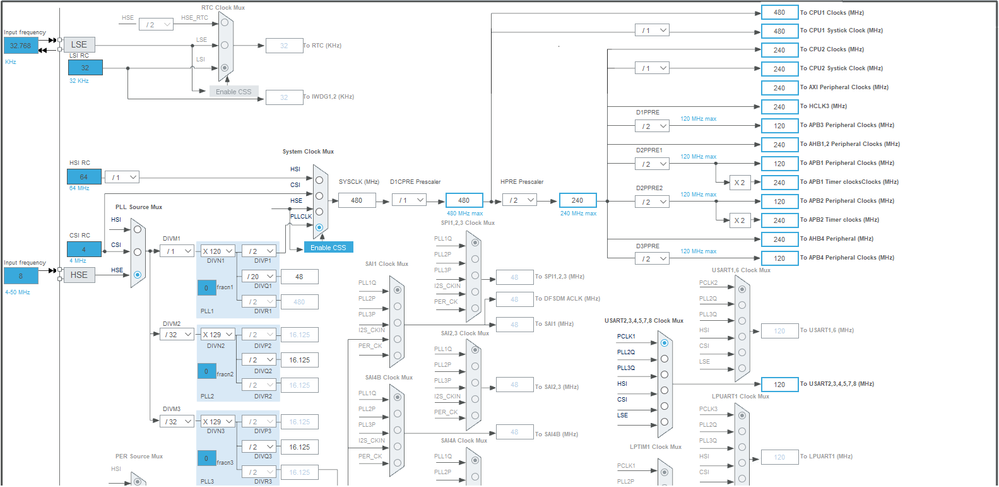

Hi guys, I tried to setup frequencies for cores to max which is possible. The code for LL was generated, compiled, but the actual frequency of core M7 (480 MHz) looks much lower than 480 MHz.

LL generated code

void SystemClock_Config(void)

{

LL_FLASH_SetLatency(LL_FLASH_LATENCY_4);

if(LL_FLASH_GetLatency() != LL_FLASH_LATENCY_4)

{

Error_Handler();

}

LL_PWR_ConfigSupply(LL_PWR_DIRECT_SMPS_SUPPLY);

LL_PWR_SetRegulVoltageScaling(LL_PWR_REGU_VOLTAGE_SCALE0);

LL_RCC_HSE_EnableBypass();

LL_RCC_HSE_Enable();

/* Wait till HSE is ready */

while(LL_RCC_HSE_IsReady() != 1)

{

}

LL_RCC_PLL_SetSource(LL_RCC_PLLSOURCE_HSE);

LL_RCC_PLL1P_Enable();

LL_RCC_PLL1Q_Enable();

LL_RCC_PLL1_SetVCOInputRange(LL_RCC_PLLINPUTRANGE_8_16);

LL_RCC_PLL1_SetVCOOutputRange(LL_RCC_PLLVCORANGE_WIDE);

LL_RCC_PLL1_SetM(1);

LL_RCC_PLL1_SetN(120);

LL_RCC_PLL1_SetP(2);

LL_RCC_PLL1_SetQ(20);

LL_RCC_PLL1_SetR(2);

LL_RCC_PLL1_Enable();

/* Wait till PLL is ready */

while(LL_RCC_PLL1_IsReady() != 1)

{

};

/* Intermediate AHB prescaler 2 when target frequency clock is higher than 80 MHz */

LL_RCC_SetAHBPrescaler(LL_RCC_AHB_DIV_2);

LL_RCC_SetSysClkSource(LL_RCC_SYS_CLKSOURCE_PLL1);

LL_RCC_SetSysPrescaler(LL_RCC_SYSCLK_DIV_1);

LL_RCC_SetAHBPrescaler(LL_RCC_AHB_DIV_2);

LL_RCC_SetAPB1Prescaler(LL_RCC_APB1_DIV_2);

LL_RCC_SetAPB2Prescaler(LL_RCC_APB2_DIV_2);

LL_RCC_SetAPB3Prescaler(LL_RCC_APB3_DIV_2);

LL_RCC_SetAPB4Prescaler(LL_RCC_APB4_DIV_2);

LL_SetSystemCoreClock(480000000);

/* Update the time base */

if (HAL_InitTick (TICK_INT_PRIORITY) != HAL_OK)

{

Error_Handler();

};

LL_RCC_SetUSARTClockSource(LL_RCC_USART234578_CLKSOURCE_PCLK1);

LL_RCC_SetUSBClockSource(LL_RCC_USB_CLKSOURCE_PLL1Q);

}The clock diagram in CubeMX

- Labels:

-

RCC

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 6:02 AM

> LL_RCC_HSE_EnableBypass();

It looks like you're using a clock signal as the HSE input. The chip has no way to validate that this signal is at the 8 MHz you say it is. It's possible the clock is at a different frequency than you think.

What clock speed are you seeing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 8:38 AM

But HSE source should come from stlink osc am I right? Because X2 is not soldered.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 8:43 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 8:51 AM

Yes sorry, Im using nucleo-h755zi-q dev board.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 12:17 PM

So If the source is 8Mhz, this configuration should be correct or?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-18 2:06 PM

Seems fine to me, but I did not study it.

You can use HAL_RCC_GetSysClockFreq to see what comes back.

Also seems reasonable to look at the RCC registers directly and see what is amiss. There aren't that many relevant registers here.