- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: [STM32H743VI, RM0433] Is the formula to calcul...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[STM32H743VI, RM0433] Is the formula to calculate the WWDG timeout wrong?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-17 03:24 AM

I have recently faced with problem that the real timeout and calculated aren't equal.

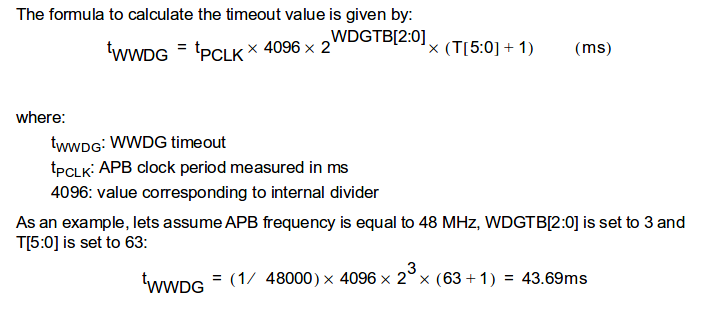

The formula is described as in the screenshot below.

But the WWDG initiates a reset when the counter (T[5:0]) changes value from 0x40 to 0x3F. Then we have only 128 - 64 (0x40) counts until a reset occurred. Shouldn't the formula be like t_wwdg = t_pclk * 4096 * 2 ^ (WDGTB[2:0]) * (T[5:0] + 1 - 0x40) ?

Solved! Go to Solution.

- Labels:

-

IWDG-WWDG

-

STM32H7 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-17 01:05 PM

One thing that you don't seem to have spotted is that you write T[6:0] to the counter, not T[5:0] with T[6] always set*, but the formula gives the timing from T[5:0].

And it is when bit 6 drops from 1 to 0 that the WWDG fires.

T[5:0] cannot express 0x40 -- it needs to be T[6:0]

So a long-as-possible counter write of 0xFF will have 0x3F in T[5:0]

*And WDGA set which is in bit 7

Hope this helps,

Danish

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-17 01:05 PM

One thing that you don't seem to have spotted is that you write T[6:0] to the counter, not T[5:0] with T[6] always set*, but the formula gives the timing from T[5:0].

And it is when bit 6 drops from 1 to 0 that the WWDG fires.

T[5:0] cannot express 0x40 -- it needs to be T[6:0]

So a long-as-possible counter write of 0xFF will have 0x3F in T[5:0]

*And WDGA set which is in bit 7

Hope this helps,

Danish

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-09-17 11:53 PM

Indeed! I didn't expected this at all. Then this topic should be closed I think, since there is no mistake.

Tanks for clarification, Danish!

- Watchdog timer selection for Project in STM32 MCUs Products

- What can cause UART overrun error while using DMA for reception? in STM32 MCUs Products

- STM32H56 PKA Arithmetic operations not working in STM32 MCUs Security

- Nucleo-WL55JC1 to Custom PCB STM32WL55 UART Communication Not Working. in STM32 MCUs Wireless

- code stop in function HAL_I2C_IsDeviceReady in STM32CubeIDE (MCUs)