- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32H563ZIT6: DMA register config problem wit...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H563ZIT6: DMA register config problem with different Keil optimization level

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-07-31 02:02 AM

Dear Community,

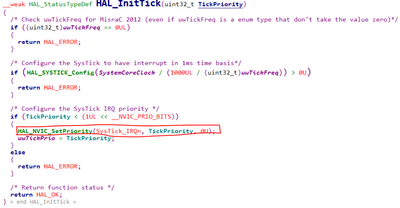

I am currently using NUCLEO144-H563ZI board with STM32H563ZIT6 microcontroller to get ADC data via GPDMA1_CHANNEL1. The problem occurs when I change the optimization level in Keil(MDK-ARM version 5.26.2.0). If the firmware is compiled at optimization level O1, the DMA operate well and data can be read from destination memory. But if the firmware is compiled at optimization level O0, the DMA seems to be stuck in BUSY status. I simulate the process using Keil and find that if I comment out the code in red block in stm32h5xx_hal.c, the DMA can operate well even if at optimization level O0. Please see picture below.

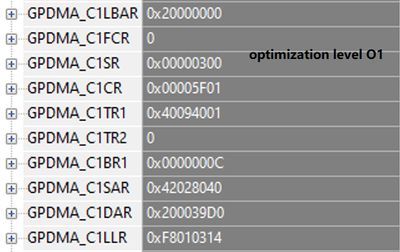

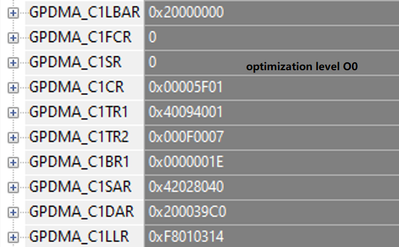

Additionally, I find that the DMA register configuration is different at these two optimization level. Please see pictures below.

And the DMA initialization code as below:

- Labels:

-

DMA

-

STM32H5 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-07-31 06:07 AM

Probably the bug is in other parts of your code, not the initialization. How are you using the DMA? Post a complete example which exhibits the problem.

The difference in C1SR values reflect the HT and TC flags are set in the top example, but not in the bottom. This is consistent with the DMA still being busy.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-08-05 07:37 AM

Hi All,

This post has been escalated to the ST Online Support Team for additional assistance. We'll contact you directly.

Regards,

Jake

ST Support

- STM32cubeMX generate wrong makefile in STM32CubeMX (MCUs)

- STM32WE5 SubGHz_Phy Middleware Questions in STM32 MCUs Wireless

- The LPBAM scenario fails to be created after the HAL update. in STM32 MCUs Products

- STM32H7 optimized SPI driver for use in DMA mode in STM32 MCUs Products

- elf has a LOAD segment with RWX permissions w/ Optimization in STM32CubeIDE (MCUs)