- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32G0x1 Alternate Functions Clarification

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32G0x1 Alternate Functions Clarification

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-07-05 2:04 PM

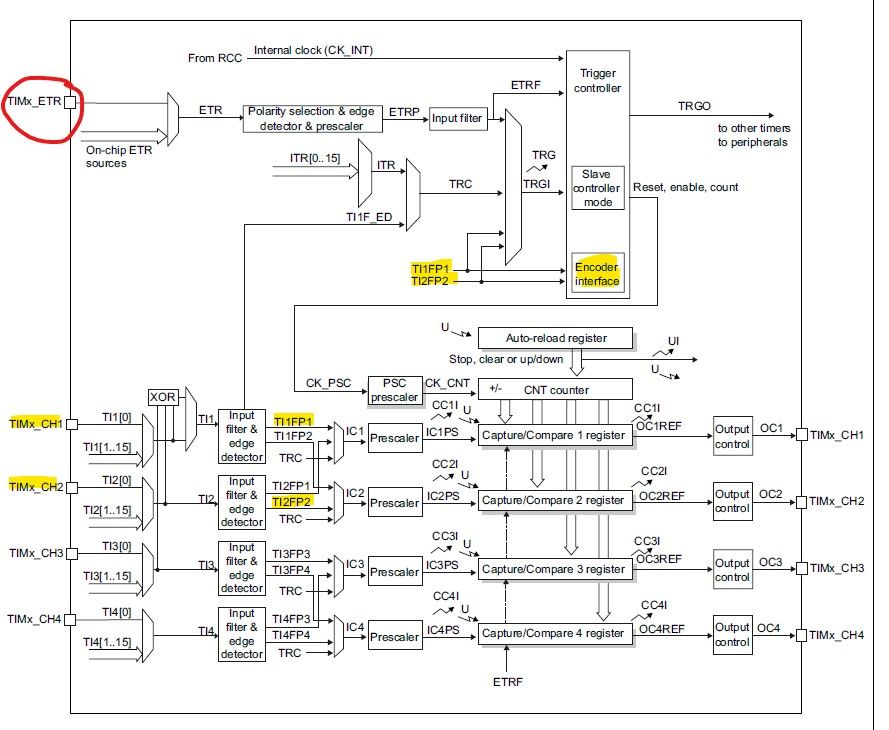

I am designing a board and would like to use the 32 bit timer (TIM2) in encoder mode. Per the block diagram in RM0444:

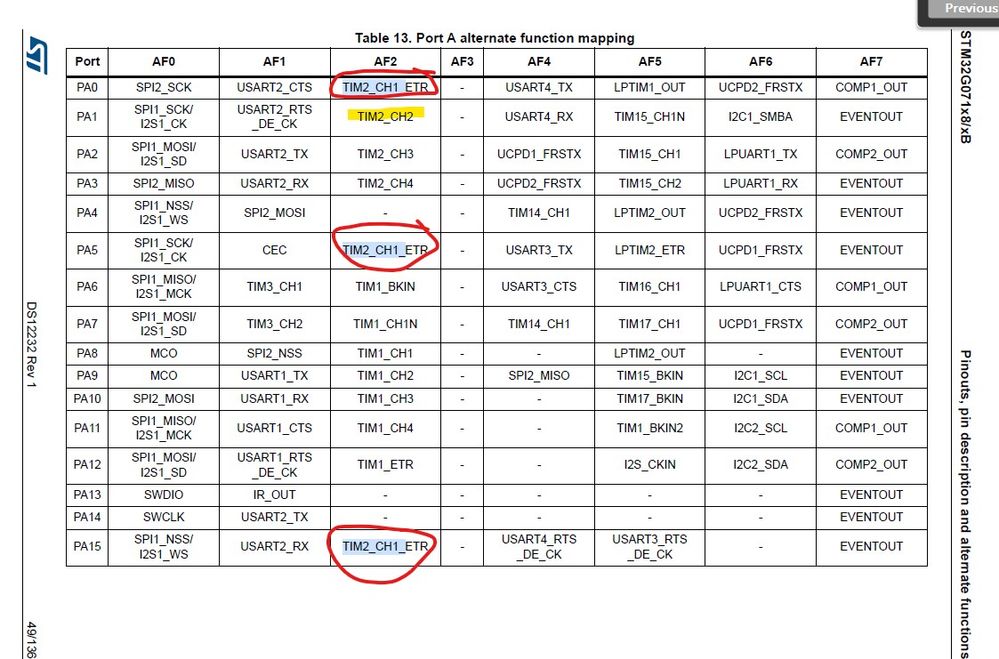

However, in the STM32G0x1 data sheet alternate functions table, I see:

I reference register TIM2_AF1 (p. 694 of RM0444), and there are a number of different ETR sources - but none are TIM2_CH1.

What am I missing?

- Labels:

-

Documentation

-

STM32G0 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-07-05 2:29 PM

> which is it? TIM2_CH1 or TIM2_ETR? How can it be both?

Input from that pin is simply connected to both the ETR and CH1 inputs of the TIM module.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-07-06 5:09 AM

Jan,

Thanks for the prompt response. To confirm, the RM implies that external trigger and encoder modes are mutually exclusive (per SMS bits in TIMx_SMCR). So if I connect my external encoder signals to PA0 (TIM2_CH1_ETR) and PA1 (TIM2_CH2), I should be able to configure the registers to enable TIM2 (32 bits) to act in encoder mode. Is that correct?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-07-06 5:23 AM

> So if I connect my external encoder signals to PA0 (TIM2_CH1_ETR) and PA1 (TIM2_CH2), I should be able to configure the registers to enable TIM2 (32 bits) to act in encoder mode. Is that correct?

Yes.

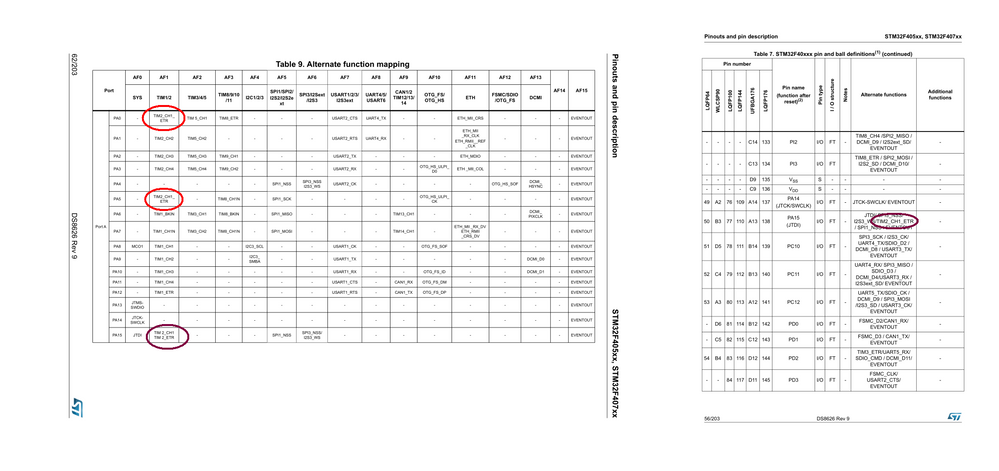

The TIM2_CH1_ETR combination is quite common in all other STM32, too. This used to be a recurring question one time. The DS used to marke these pins more sanely, but then ST somehow messed it up completely.

An entirely random selection of related threads (you can find more if you want):

https://community.st.com/s/question/0D50X00009XkgkeSAB/stm32f407-tim2ch1etr

https://community.st.com/s/question/0D50X00009XkZNISA3/where-is-tim2ch1-on-the-stm32f4-chips

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-07-06 5:31 AM

#Documentation

#what_a_mess

PS. In the CubeMX xml files, the TIM2_CH1 and TIM2_ETR functions are given separately. That explains the decrease of complaints: most users don't read DS these days.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-07-06 6:48 AM

Thanks again. Have to love documentation inconsistencies...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-12-20 1:20 PM

Do I understand correctly that with an active AF1 remap, the signal from the physical pin is multiplexed to the CH1 input of the timer channel and simultaneously to the ETR input of this timer?

Do I understand correctly that the same AF1 remap also determines the CH1 output of the timer channel on the same physical pin?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-12-20 2:46 PM

Yes and yes. For STM32 timers an input and output is on the same TIMx_CHx pin.

- STM32H5 JTDO/TRACESWO pin not working as UART7_RX despite alternate function support in STM32 MCUs Products

- UART Interrupts With Nucleo-L476 in STM32 MCUs Embedded software

- Clarification on Secure Boot Flow with PCROP Protection for STM32H723 in STM32 MCUs Security

- STM32U5 UART: Unexpected Dependency on HAL_HalfDuplex API for RS485 Operation in STM32 MCUs Products

- STM32H753 QUADSPI – Clarification on Dual Bank, IO Lines, and Multi-Flash Possibilities in STM32 MCUs Products