- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F7 FMC Synchronous CLKDIV=3

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F7 FMC Synchronous CLKDIV=3

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-10 8:24 AM

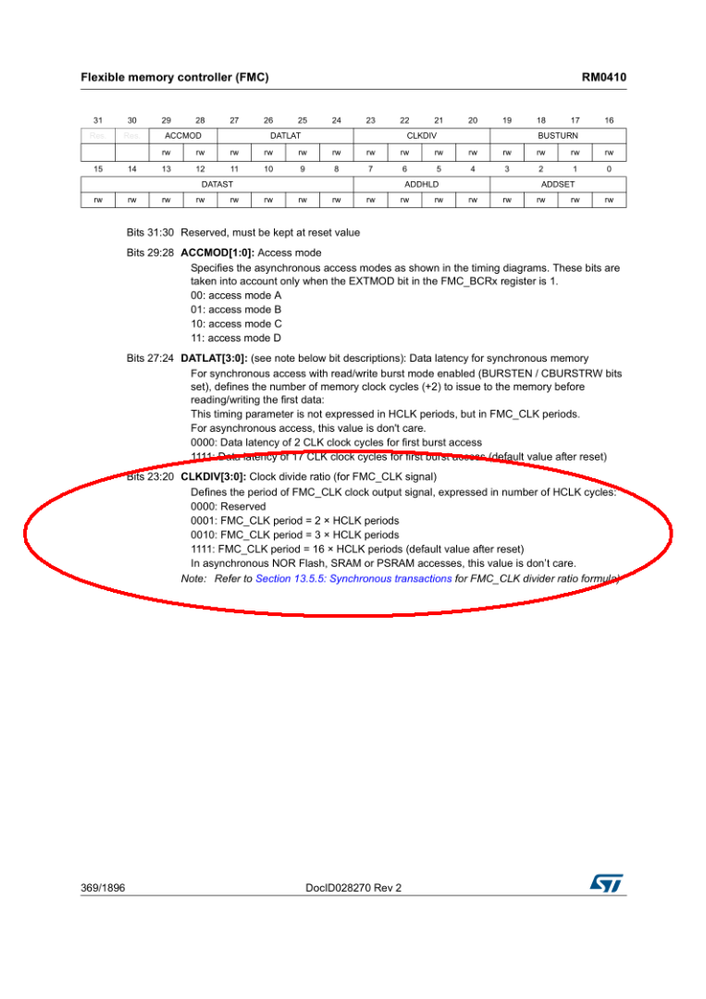

I'm looking to use the FMC in Synchronous PSRAM 16-bit mode, and need to run CLKDIV of 3 (or 4). The reference manual (RM0410) waveforms seem to show only a setting of CLKDIV=2. In figure 50/51, CLK is shown toggling every rising HCLK edge. How does it behave when CLKDIV=3?

For example, in figure 50, NADV is low for 2 HCLKs, or 1 CLK period, and AD[15:0] is valid for 2 HCLKS before, and 1 HCLK after NADV rising edge. How does it behave when CLKDIV=3?

Thanks,

-Paul

#stm32f7 #fmc #clkdiv- Labels:

-

FMC-FSMC

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-10 9:05 AM

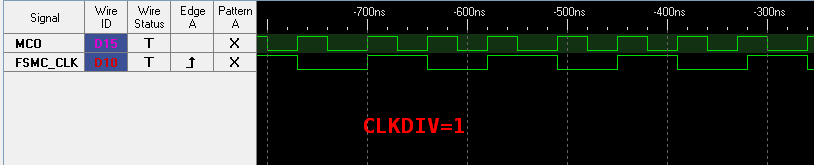

The reference manual (RM0410) waveforms seem to show only a setting of CLKDIV=2.

IMO they show setting of CLKDIV=1:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-10 10:37 AM

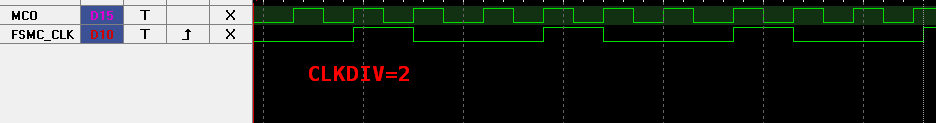

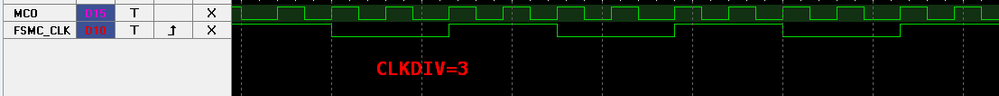

This was on STM32F407 and not and 'F7, but I believe it will be similar.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-10 1:47 PM

JW - Yes, I meant HSECLK/2 (CLKDIV=1). Your waveforms are helpful, thanks.

Do you know the NADV relationship in a CLKDIV=2 (HSECLK/3) scenario? Figure 50 shows 3 HSECLK cycles from NADV falling edge to the start of DATLAT.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-10 3:54 PM

Sorry, no. I understand that the FMC chapter in RM is severely lacking in the details.

I'd recommend you to take a Nucleo board, and 'dry' configure it for the required FMC mode and take the waveforms (I don't have a F7 Nucleo at hand, and the Discos are limited by the existing on-board circuitry - nor have I the time :-()

Other option is to contact ST through FAE or the web support form.

JW

- STM32H755 HR timer synchronization with general purpose timers in STM32 MCUs Products

- Synchronizing PWM Signal through an external Signal in STM32CubeIDE (MCUs)

- STM32F7 Discovery kit + FMC SDRAM in STM32 MCUs Embedded software

- CUSTOM BOOTLOADER in STM32 MCUs Embedded software

- Interfacing ATWINC3400 Wi-Fi Module with STM32F7 (SPI & Driver Modifications) in STM32 MCUs Embedded software