- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F7: Can I use ADC conversions at highest ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F7: Can I use ADC conversions at highest speed (2.4Msps) with 216MHz clock?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 11:46 AM

I'm currently using an STM32F4 board for a project that requires fast ADC conversion (2.4msps per channel, all 3 channels simultaneously) *and* pretty extensive cross correlation. Due to the clock tree of the F4, if I want to use the highest ADC clock, I need to run the F4 at 144MHz instead of 168MHz, making all the cross correlation code slower than it could be.

I'm thinking of moving to an F7 board (Nucleo767), for the additional RAM and much faster core/DSP. But playing with the clock tree of the F7 in STM32CubeMX, I seem to bump into the same limits as the F4, where I need to use 144MHz in order to get a 36MHz ADC clock, and there is no prescaler that works for 216MHz, making it even worse (in proportion) than the F4 loss (I know it would still be faster overall, but running at 144MHz vs 216MHz is a significant difference)

Is there any way to run 2.4Msps on an F7 with a 216MHz clock?

- Labels:

-

ADC

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 12:37 PM

Maybe go boldly to:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 1:02 PM

The same when You want to use USB at 48 Mhz.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 1:48 PM

Actually, according to STM32CubeMx there is a solution for 216MHz with 48MHz USB clock (PLLM=4, PLLN=216, PLLP=2, PLLQ=9).

It's the ADC that doesn't have a /3 prescaler, only 2 and 4 (obviously), so needs a 72MHz multiple

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 2:23 PM

Now that's interesting... there's even a cheap Nucleo board for it, so worth looking it. The main downside for me is that there seems to be only the HAL libraries for it, no LL library. I've seen a lot of bugs in HAL (in the past at least), and I find it massively confusing compared to using lower level register access

Also, CubeMX doesn't seem to be able to find a clock solution for 8MHz HSE input and 400MHz max speed (8MHz is what the Nucleo board uses). But by using this as a starting point, I managed to find something that seems to work https://visualgdb.com/tutorials/arm/stm32/stm32h7/. Yet another reason to dislike the HAL, I guess :)

The H7 is incredibly flexible, so it looks as if I can get everything I need: 36MHz ADC, 48MHz for the USB, and 400MHz clock for maximum math performance.

Very nice suggestion thanks! Since I need to buy a Nucleo board one way or another, might as well go this way (if I manage to get dragged into 2019 and accept the HAL, that is :)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 4:05 PM

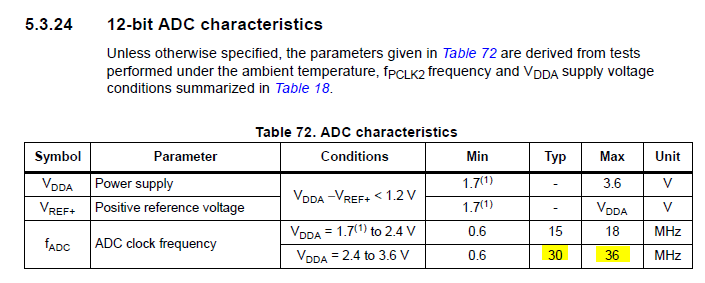

Hi @fbar , according with the STM32F767 datasheet maximum clock frequency of the ADC clock is 36Mhz:

The ADC speed is not directly related with the main core clock, this is the reason because the cubeMX always select to you 36Mhz :grinning_face: .

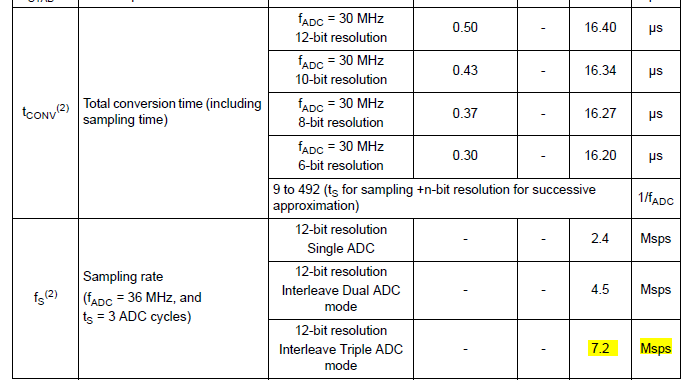

There is a way to speed up the rate of conversion and it's using the interleave mode, according with the datasheet those are the rates that you can reach:

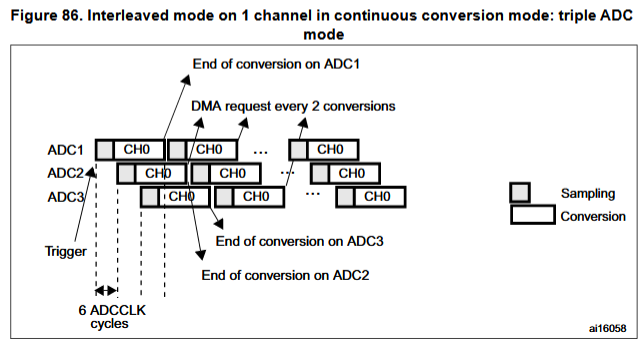

About 7,2Msps, I tested it with the NucleoL476 and it really works (Even with only 2 ADC modules working, not 3). If the resolution its nor critical you could also speed up a quite more decreasing it (8 bits for example. This is the way that works the interleave mode:

Setting it in parallel with the DMA module works fine. There in the CubeMX files you can find a example project to set it.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 4:58 PM

Yes, I understand all of that pretty well, thanks. I spent 3 days poring over every scrap of information for the F4, and doing all sort of tests, instrumented with an oscilloscope. That doesn't help me much, though

First of all, there's no way to generate a 36MHz clock from any combination of prescalers and divisors if you select a 216MHz clock on a Nucleo board with 8MHz crystal (it might be possible with different crystals, haven't tried all combinations, but I doubt it). The only way to get a 36MHz ADC clock is to use a core clock of 144MHz. Try selecting the Nucleo F467 board in CubeMX and see if you can get a 36MHz ADC clock on the ADC. ADCLK uses PCLK2, and can use a 2 or 4 divider (higher, too, but not relevant here) , so since PCLK2 is 108MHz with a 216 core clock, you can only use a 4 divider, resulting in a 27MHz clock at best, decreasing the maximum sample rate to 1.8Msps from 2.4Msps per second. There's no /3 prescaler that can be used to get to 36MHz from 108MHz. not with the F4 or F7 clock tree (can be done with the H7, as pointed out)

Also, since, as I explained in my original question, I need to use all 3 ADCs at once (I'm actually sampling 6 channels, two per ADC, using triple regular scan mode), so can't use the triple interleaved mode. My actual ADC conversion rate is half the maximum possible, since each ADC channel must convert 2 separate samples. So from a theoretical 1.2Msps for all 6 channels (half the max 2.4Msps) I drop to 900K samples per second

And I really need at least 12 bits to have any hope to get a decent cross correlation between signals at those speeds. So I'm back to square one even with the F7 (which is better than the F4 in the sense that I can get 27MHz ADC clock instead of 21MHz clock at the maximum processor speed of respectively 216 and 168)

Or do what I'm doing now, dynamically changing the core clock from 144MHz to 168MHz once the ADC conversion is finished, but that seems to mess up the USB libraries and decrease USB reliability

The H7 looks like a winner, on the other hand

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 5:10 PM

Bummer, I knew that there *had* to be something not quite right :) it's a classic. While the F4 and F7 support triple regular scanned ADC (allowing me to sample 6 channels in perfect sync, well, 3 channels are slightly offset, but I know how to compensate for that), the H7 only supports dual regular conversion mode for ADC1 and ADC2, plus an independent ADC3. I need to do some more digging and see if that's a problem, since I will in any case use TIM2 TRGO to trigger the conversion. As long as the channels are close enough, my microphone array calibration (which is there to deal with small errors in the microphone placement) can take care of this, too. Need more digging in the manual... what's 3247 pages of reference between friends? Gosh, that chip is a true monster. Luckily the ADC portion is barely more than 100 pages

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 9:07 PM

Not for ~F4 (407) where your have 168 Mhz max.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-03-29 9:12 PM

Very interesting topic. What is the solution to max core, max adc, usb clocks. For H7, F4, F7.

- ADC: DMA of injected conversions does not work, when there are no regular conversions in STM32 MCUs Products

- TouchGFX for STM32H750B DK Board in STM32 MCUs Boards and hardware tools

- Reference value and sequence sampling in STM32U585. ADC problem? in STM32 MCUs Products

- STM32F7 ADC + DMA + multiples channels + regular conversion + continuous conversion not sampling in STM32CubeMX (MCUs)

- UART DMA not work with STM32F767ZI and STM32F745VE in STM32CubeMX (MCUs)