- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: QSPI (QuadSPI) as General Purpose "Parallel" S...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

QSPI (QuadSPI) as General Purpose "Parallel" SPI with MISO and MOSI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-22 11:43 AM

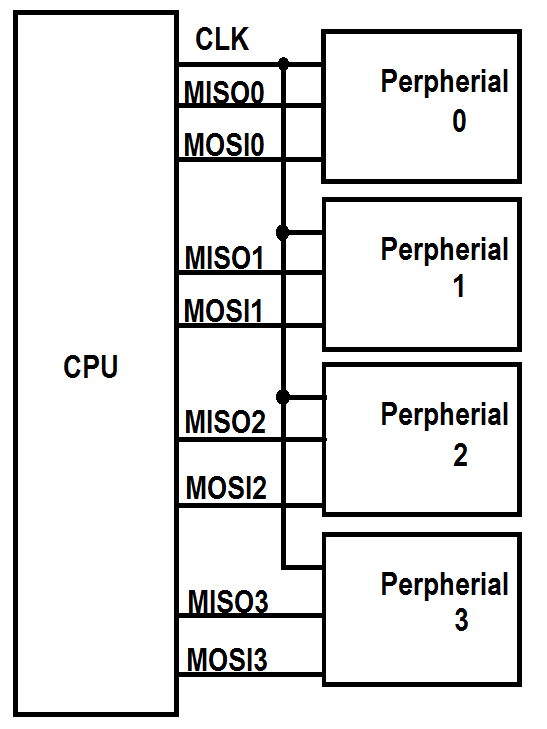

I'm evaluating the STM32H742x and its cousins. My design has four identical high bandwidth SPI based analog front-end peripherals, each peripheral with its own MOSI and MISO. I would like to command them with in a concurrent fashion (analogous to SIMD) using a common DMA driven CLK, but a per peripheral MISO/MOSI (full duplex).

Is the QuadSPI on the STM32H742x family flexible enough to support this? Where should I start looking in the docs for how to do this?

- Labels:

-

QSPI

-

SPI

-

STM32H7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-22 12:05 PM

What is the reason here?

Use multiple SPI memories to emulate a QSPI memory?

Higher bandwidth?

Price optimisation?

High frequency level shifting (mono directional lines)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-22 12:32 PM

Several reasons, I'm out of spi ports if I use a unique SPI port for each as I have several other concurrent SPI activities going on to other SPI peripherals, I need to synchronize my slave spi devices as they all trigger off of the same SPI command. The commands (CPU MOSI) could probability be driven from a single line MOSI line, but the MISOs need to be received in parallel by the CPU.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-22 1:43 PM

Check the corresponding RM. Note that either all four data lines (or all eight in dual mode) are in output mode or all are in input mode when QPI mode is used. In SPI mode you have MISO/MOSI simultaneously, but only one pair (single) or two (dual mode). And even then, either data is send or received, not "exchanged" simultaneously. Transfer sizes are restricted, only 8-bit multiples (there are exceptions: dummy cycles, but with no data transfer).

Transfer always works this way: send 0 to 4 bytes (command) to peripheral, then 0 to 4 bytes to peripheral (address), then 0 to 4 bytes (alternate) to peripheral, then optionally dummy clocks, and finally either receive (arbitrary amount of bytes) payload from peripheral or send (arbitrary amount of bytes) payload to peripheral. For each phase it's possible to individually select use of one, two or four data lines.

In dual flash mode the command, address and alternate bytes and dummy clocks go to both peripherals simultaneously (identical data!), then the payload is byte-interleaved from/to both peripherals.

If you connect a single MOSI line to all four peripherals and the four MISO lines to the four data lines separately, don't forget that each byte received will contain 2 bits from each device. The CPU will have to split and shift the pieces into place to reassemble the data ...

Bear in mind that the QuadSPI interface was developed with NOR flash in mind. Maybe your use case could fit, but you have to check that carefully.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-22 1:53 PM

Thanks. The more I look at it, the more I think QSPI is a poor match. Not sure why QSPI has the "SPI" in the name. Really, no connection.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-04-23 12:37 AM

The RM is quite clear (e.g RM0410) about that:

"14 Quad-SPI interface (QUADSPI)

14.1 Introduction

The QUADSPI is a specialized communication interface targeting single, dual or quad SPI

Flash memories.",

so no reason to blame ST for inappropriate statements. The term QSPI or QUADSPI isn't a particular ST wording. Other manufacturers use the very same, with similar functionality, sometimes with more functionality, but I haven't come across one which would work easily in a way you expect. See e. g. SAM E-70, LPC4300 (SPIFI), Kinetis K82. You might have a look at NXP's (Freescale's) Kinetis series, maybe the FlexIO would do the job.

- Problem while generating code with MDK-ARM in STM32CubeMX (MCUs)

- STM32CubeIDE Code Generation Always Runs in STM32CubeIDE (MCUs)

- Schematic Review Request for Custom Board Based on MB1389E in STM32 MCUs Wireless

- When I get connected and paired to peer HAL RNG doesn' work in STM32 MCUs Wireless

- VSCode code generation - CMake issue with CubeMx in STM32CubeMX (MCUs)