- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: 'OCx fast' in One-pulse mode

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

'OCx fast' in One-pulse mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-31 01:58 AM

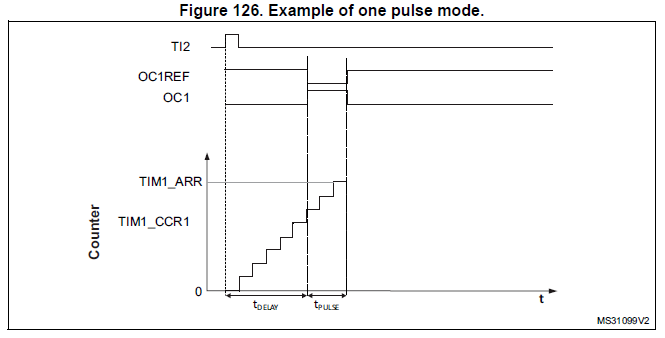

I'm using STM32F429x. I'm confused by the 'OCx fast' setting when using the 'One-pulse mode' of the timer. In DM00031020 section 17.3.15, it states:

In One-pulse mode, the edge detection on TIx input set the CEN bit which enables the

counter. Then the comparison between the counter and the compare value makes theoutput toggle. But several clock cycles are needed for these operations and it limits theminimum delay tDELAY min we can get.

''But several clock cycles are needed for these operations...., it limits the minimum delay tDELAY min we can get'', I think it means if we don't enable OCx fast setting, we will get a delay. However, I don't understand where the delay will appear in the figure above?

Anyone can explain the situation more clearly? What we can benefit from enabling �OCx fast'????

#ocx-fast #one-pulse #pwm- Labels:

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-31 11:54 AM

Hello!

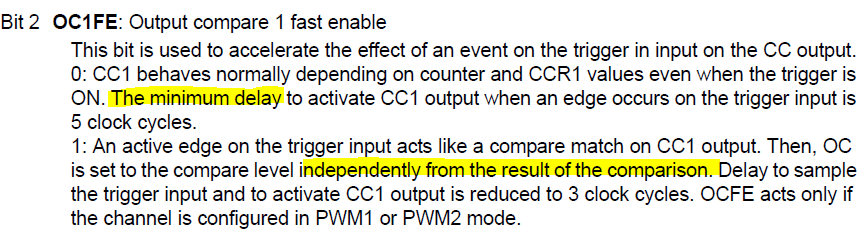

Here is the OCxFE flag

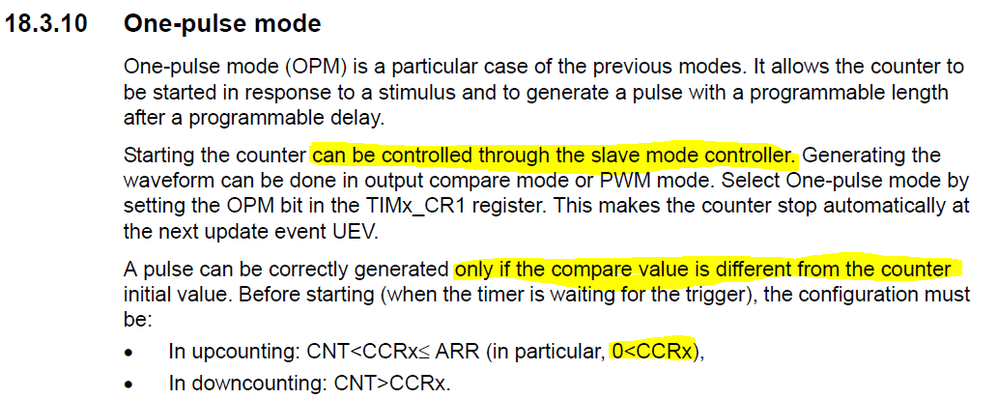

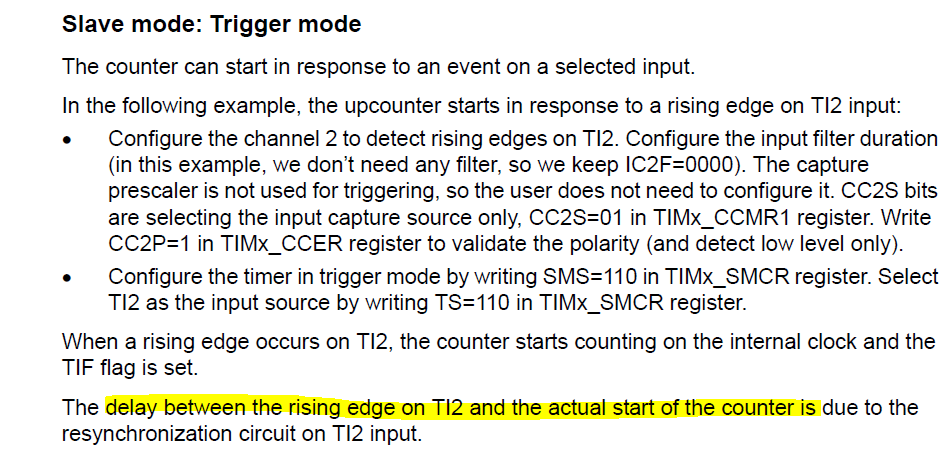

here is explained that the one pulse mode is part of slave functionality

and here is explained that this delay is due to the resync cirquit(slave functionality)

An interpretation could be The minimum delay from trigger to output is 5 clocks from internal delay plus one counter period (PreSCaler involved)

So if you want to trigger a pulse ''right now'' in one pulse mode , you must wait 5clcks +1 counter period.

In this case you can minimize the delay by set the OCfast bit, to 3 clocks only. (and no one counter period )

Regards

vf

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-08-31 10:52 PM

Thanks for your detailed explanations.

Let me make sure:

- When OCxFE = 0: Becuase CCRx must be greater than 0, so the minimum delay is 1 counter period. And plus the 'inherent' delay of STM32, the minimum delay between the trigger and our desired pulse we can achieve is 5 clocks + 1 timer counter period.

- When OCxFE = 1: The CCRx value is meaningless now, because the '

comparasion

' is bypassed now. And theminimum delay between the trigger and our desired pulse we can achieve is 3 clocks.

'clocks' counted in HCLK? Or APBx_CLK???

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-01 02:20 AM

I see. Thi is IMO confusion in terminology: One Pulse as feature set by TIMx_CR1.OPM, i.e. automatic CEN clear upon update (which is independent on OCxM settings); versus 'I want to see one pulse on the output'.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-01 02:45 AM

'clocks' counted in HCLK? Or APBx_CLK???

Probably internal timer clocks, i.e. the clock incrementing the prescaler/counter == ABP or 2xAPB depending on how did you set the APB divider.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-01 02:47 AM

Hello.

For the third question , the clock is APB but for timers there is a multiplier which value depends to APB prescaler.

Take a look at clock tree in RM0090.

To use OnePulseMode and set OCfast , OPM must be allready configured in PWM1 or 2 modes and not in Output Compare mode.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-01 03:19 AM

OPM must be allready configured in PWM1 or 2 modes and not in Output Compare mode.

I don't understand. What do you mean, in terms of timer registers?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-09-01 03:57 AM

hello!

By write at CCMRx, OCxM 0b111 for PWM mode 2 or 0b110 for mode 1.

One pulse mode can be setup in PWM or in compare output mode. ( OCxM= 0b001)

- How to test ST25DV NFC FTM mode transaction with MCU integration in STM32 MCUs Products

- long padding phase with ISM43362 on a BL475 discovery board in STM32 MCUs Products

- Timer output influenced by other timer in STM32 MCUs Products

- SPI NSSP on STM32F767ZI in STM32 MCUs Products

- Filex writing performance in STM32 MCUs Embedded software