- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- NUCLEO-H503 Timer

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

NUCLEO-H503 Timer

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-21 3:25 AM - edited 2023-07-21 3:25 AM

Hello.

I am using the NUCLEO-H503 board, and I would like to verify its speed-related specifications accurately.

I am attempting to toggle a GPIO pin using the Timer NVIC whenever the HAL_TIM_PeriodElapsedCallback() signal occurs.

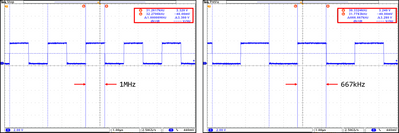

Currently, my board's clock is set to SYSCLK=250MHz, and the timer period is set to 1MHz (Prescaler=24, Counter period=9). However, I have encountered two issues:

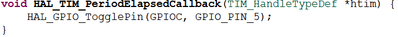

1. When I don't use the ICACHE feature, the periodicity of the callback function is not accurate. With the ICACHE feature enabled, it measures precisely at 1MHz. However, without using the ICACHE feature, it measures at approximately 666kHz.

It seems that turning on ICACHE is necessary for precise timer operation. However, in a previous inquiry about the DAC, I received an answer stating that ICACHE should be disabled to use the DAC function.

( https://community.st.com/t5/stm32-mcu-products/using-dac-of-nucleo-h503rb/td-p/572193 )

2.The Timer period is not accurate. When I set the period to 1MHz, it measures correctly, but when I set it to a higher frequency, the Timer's operation becomes inaccurate. For example, when I changed it to 2MHz with Prescaler=4 and Counter period=9, it actually operates with an interval of 1.18MHz.

Please help me find the causes of the issues I have encountered and suggest possible solutions.

Thank you.

- Labels:

-

Interrupt

-

STM32H5 series

-

SysTick

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-21 6:08 AM

Hi @sh.lee,

First of all, I think you are just seeing an artefact when ICACHE is enabled. I guess your source code is small to fit entirely (or close to) with ICACHE size (8KB). At each TIMER interrupt, when ICACHE is enabled you don't need to access to the Flash. On the contrary, when ICACHE is disabled you always need to access to the Flash when you execute the the TIM_IRQ which is quite big...

By adding further code later, you will see the same behavior even if ICACHE is enabled like you will miss (TIM_ISR will not be loaded inside the ICACHE).

As a solution:

- Trigger a DMA to write inside the GPIO BSRR register

- Use an output channel of the timer by using Output compare or PWM

Best Regards,

Gwénolé

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-07-22 12:25 AM

1 MHz interrupt frequency is quite high, much too high if HAL is involved. It gives only 250 clock cycles for the whole interrupt handling - very hard to achieve. There is nothing wrong with the timer, it's just the processor is too slow to execute the ISR in time, so it's missing some interrupts. Enabling the cache speeds it up a little.

Firing the interrupt with 1 MHz frequency is usually a bad idea. With HAL servicing the interrupts it is simply impossible due to HAL overhead.

- Program does not run on STM32f407VET - CubeIDE not generating timebase IRQ handler for different timebase source. in STM32CubeMX (MCUs)

- PWM input output drift in STM32 MCUs Products

- STM32H753ZI / MDMA issue with linked list (DMA ADC) in STM32 MCUs Embedded software

- STM32G474 Timer X register update behaviour when CONT=0 with RETRIG=1 in STM32 MCUs Products

- Arbitrary waveform by timer using DMA in STM32 MCUs Embedded software