- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Master/Slave problem on TIM3 in STM32L476 - slave ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Master/Slave problem on TIM3 in STM32L476 - slave not counting when ITR2 selected

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-28 9:03 AM

Hello,

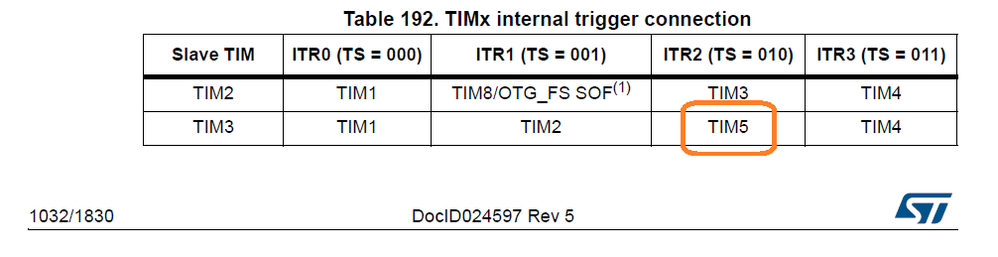

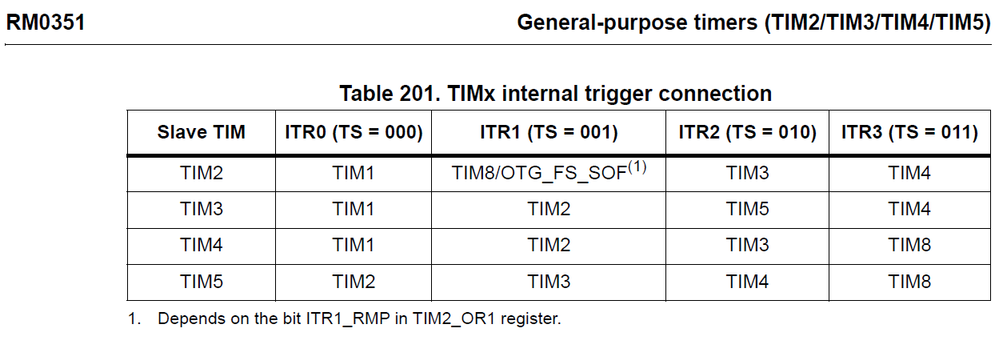

I am working on the NUCLEO-L476RG board. I am trying to use two pairs of counters in master/ slave mode. In the first chain TIM2 is the master and TIM4 is the slave so in SMCR of TIM4 ITR1 is selected and this works as expected. In the second chain TIM5 is the master and TIM3 is the slave so in SMCR of TIM3 ITR2 is selected and this does not work. Using the debugger I can see that TIM5 is counting but TIM3 is not. Also I have configured GPIO so that I can see action on oscilloscope.

I have tried setting SMCR of TIM3 to ITR0 (TIM1 master) and that works

I have tried setting SMCR of TIM3 to ITR1 (TIM2 master) and that works

I have tried setting SMCR of TIM3 to ITR3 (TIM4 master) and that works

Why does TIM3 not count when SMCR is set to ITR2 and TIM5 is master?

Reference Table 201 in RM0351

In all instances the master TIM has MMS in CR2 set to 2, UPDATE.

Thanks,

Chris

- Labels:

-

Documentation

-

STM32L4 series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-28 3:08 PM

Confirming your experience, on NUCLEO-L476RG

Here CNT at HAL_Delay(1000) intervals, TIM3 does not increment when TIM5 TRGO UPDATE is the ITR source, masters here dividing down 80 MHz to 1 Hz

TIM3: 0 TIM2: 14 TIM5: 14

TIM3: 1 TIM2: 45 TIM5: 45

TIM3: 2 TIM2: 75 TIM5: 75

TIM3: 3 TIM2: 105 TIM5: 105

TIM3: 4 TIM2: 135 TIM5: 135

TIM3: 5 TIM2: 165 TIM5: 165

TIM3: 6 TIM2: 195 TIM5: 195

TIM3: 7 TIM2: 225 TIM5: 225

TIM3: 8 TIM2: 255 TIM5: 255

TIM3: 9 TIM2: 285 TIM5: 285

TIM3: 10 TIM2: 315 TIM5: 315

TIM3: 11 TIM2: 345 TIM5: 345

TIM3: 12 TIM2: 375 TIM5: 375

TIM3: 13 TIM2: 405 TIM5: 405

TIM3: 14 TIM2: 435 TIM5: 435

TIM3: 15 TIM2: 465 TIM5: 465

TIM3: 16 TIM2: 495 TIM5: 495

TIM3: 17 TIM2: 525 TIM5: 525

TIM3: 18 TIM2: 555 TIM5: 555

TIM3: 19 TIM2: 585 TIM5: 585

TIM3: 20 TIM2: 615 TIM5: 615

TIM3: 21 TIM2: 645 TIM5: 645

TIM3: 22 TIM2: 675 TIM5: 675

..

Older manual, but consistent, and not working as described

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-28 4:54 PM

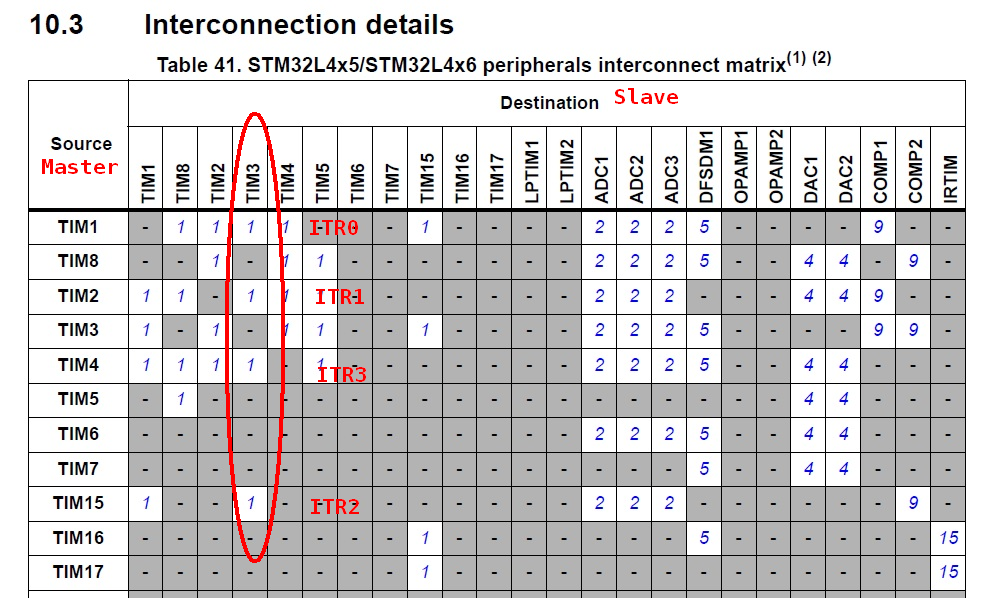

It's TIM15 not TIM5. Try.

@Imen DAHMEN can you please put it up to the list of things to fix in the documentation. Thanks.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-28 5:26 PM

Yes, TIM15 seems to be what it is, stupid docs..

TIM3: 0 TIM15: 14

TIM3: 1 TIM15: 35

TIM3: 2 TIM15: 55

TIM3: 3 TIM15: 75

TIM3: 4 TIM15: 95

TIM3: 5 TIM15: 115

TIM3: 6 TIM15: 135

TIM3: 7 TIM15: 155

TIM3: 8 TIM15: 175

TIM3: 9 TIM15: 195

TIM3: 10 TIM15: 215

TIM3: 11 TIM15: 235

TIM3: 12 TIM15: 255

TIM3: 13 TIM15: 275

TIM3: 14 TIM15: 295

TIM3: 15 TIM15: 315

..

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-28 5:34 PM

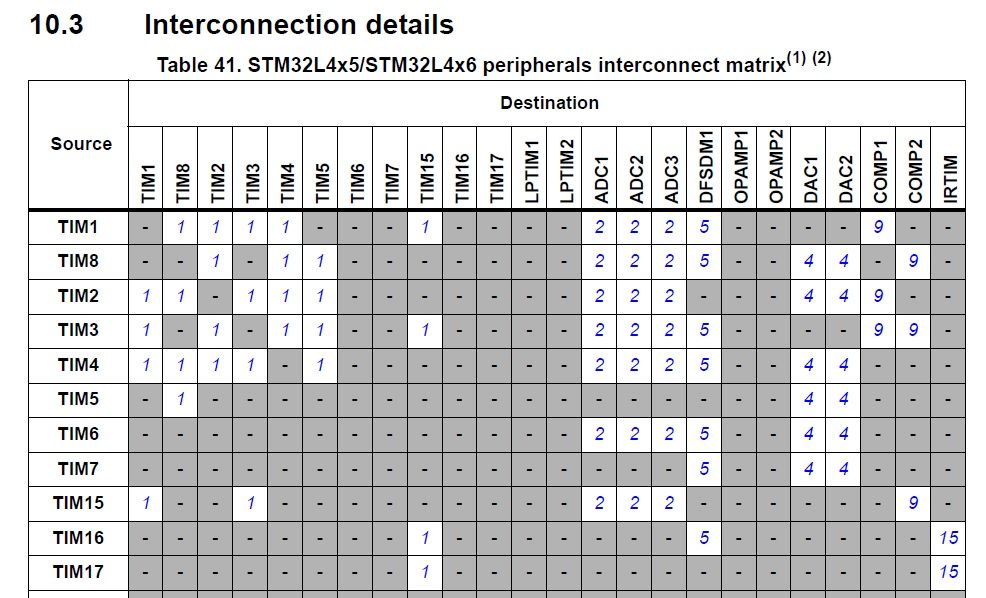

If you wonder how did I find out: remember how I always brag about the Interconnections chapter? Turns out in this case it was the one which contained the correct information...

;)

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-28 5:42 PM

Fair enough, but how does it associate with TIM3 (i see the TIM5 and TIM15 columns marked), got 5 boxes, and 4 ITR, or is that broken too?

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-28 5:46 PM

I'd guess there is a mux option for TIM5 vs TIM15, but the chapter that should explain that seems a bit vacant of such detail. Just points at other tables, which in this case has an useable option documented, doesn't say TIM5 or TIM15

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-29 1:20 AM

You have to look at the column, as it's TIM3's perspective as Slave, selected in TIM3_SMCR.TS

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-29 1:40 AM

Ok, I was playing across not down. Wouldn't this table be more useful with boxes saying ITRx?

Like playing battleships via sudoku.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-10-29 2:09 AM

In the timer section of the Reference Manual this is the information presented.

I have been looking briefly through some of the Reference Manuals for STM32F family members and there is no Interconnection details section and I have always relied on the corresponding table to that inserted above. The other families present the TIM3-TIM5 connection and so the question is why make this change for the STM32L4xx series? And why not correct the information presented in the above table, this is after all revision 6 of RM0351. The same error is present in RM0392. It might be useful to have a bit in TIM3 OR1 or OR2 that enabled TIM3-TIM5 connection, just a thought!

- STM32L476RG with Nucleo-GFX01M2 transparent font background in STM32 MCUs TouchGFX and GUI

- How to execute a program uploaded with JTAG on a target configured to start bootloader in STM32 MCUs Embedded software

- STM32L476: how to select ADC & ADC channel the DAC is internally routed to ? in STM32 MCUs Products

- Make SPI NSS hardware output produce a steady low during SPI transaction in STM32 MCUs Products

- Problem with outputting LSE clock on PA8 pin as MCO in STM32 MCUs Products