- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Known issues with D-cache and FMC on STM32F7

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Known issues with D-cache and FMC on STM32F7

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-27 6:05 AM

Hi,

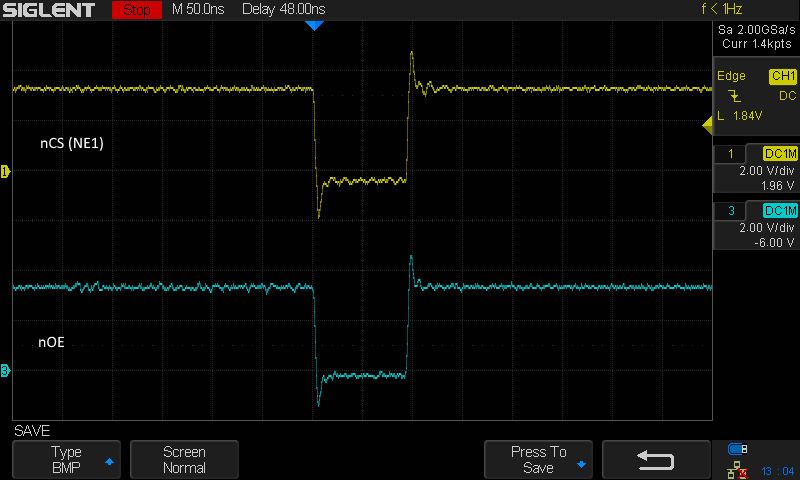

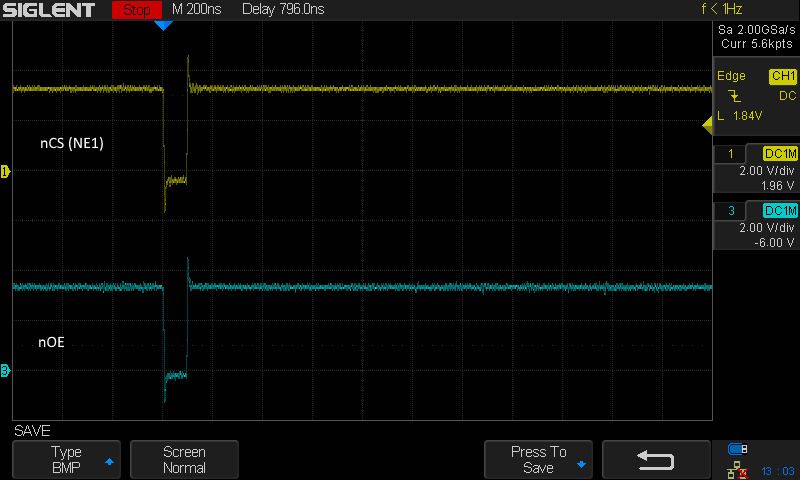

I'm using a STM32F765 clocked at 216MHz and when D-Cache is enabled it badly affects reads from a device connected via the external FMC address/data bus (NE1, 16 bit data, 10 bit address). The following pictures show the problem (note ringing is caused by non-optimum scope lead grounding)

D-Cache On:

D-Cache off (expected result & same time base as above):

I've checked the datasheets and errata but there is no mention of the issue I'm seeing. My multi-layer board is well decoupled, has ground & power planes and traces are short.

Has anyone come across this issue with D-Cache affecting FMC accesses ?

Thanks

Dave

- Labels:

-

FMC-FSMC

-

STM32F7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-11-24 4:10 AM

Hello,

I am facing same problem, FMC performs 8 instead of 1 write operation.

I have remaped FMC to 0xC0000000, but without result. Theoretically 0xC0000000 region of memory is not cacheable, so problem should be solved. Maybe there is problem with something else?

MPU configured to disable caching (for 0x60000000 and 0xC0000000) also did not work. I have tried many MPU configurations with no result, is it possible that I have missed the correct one?

I have also tried to invalidate cache data before FMC write operation, but without results.

To clarify situation:

MCU I am using is STM32H743. Ethernet, sdmmc and many other interfaces are active, so maybe there is some hardware interference?

I have observed that when I create new project with FMC only, remaping FMC bank to 0xC0000000 solves the problem. Unfortunately project I am working on is huge and additionaly made by someone else soI am afraid that recreation may result in some failures that I will not be able to recognise.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-11-24 5:55 AM

> Theoretically 0xC0000000 region of memory is not cacheable

It's not cached by default, but that can be changed in MPU.

Maybe the huge project contains MPU configuration you don't know about. Try to read out the MPU or place data breakpoints (watchpoints) to its registers to capture any writes to it.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-11-25 12:36 AM

Thank you for your answer.

I've checked MPU register and there are 3 protected regions but all of them are refering to D2 RAM region.

The problem starts to be really annoying becouse I haven't made any progress since monday.

- « Previous

-

- 1

- 2

- Next »

- [NUCLEO-N657X0-Q] ETH1 MAC/DMA not receiving packets & Memory Management Tool problems in STM32 MCUs Embedded software

- Nucleo-H755 ST-LINK MCU overheating and ST-LINK not detected in STM32 MCUs Boards and hardware tools

- STM32CubeIDE 2.1.0 released in STM32CubeIDE (MCUs)

- STM32F746G-Discovery – HardFault during LwIP Init + Netif setup in STM32 MCUs Embedded software

- Granular D-Cache maintenance operations cause artefacts or hardfaults in STM32 MCUs TouchGFX and GUI