- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: How many GPIO interrupt latency cycles from ed...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How many GPIO interrupt latency cycles from edge to IRQ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-05 2:11 AM

I know the latency of Cortex M3/M4 of interrupt is 12 cycle, I got a scenario that interrupt and DMA use same trigger edge from external. Before the DMA starts transfering, I wanna ensure that CPU will not change the data. so the IRQ must be set to make main CPU process be halted, then the dma transfering will be safe.

below picture is from (https://www.nxp.com/docs/en/application-note/AN12078.pdf) that shows the measure of edge to IRQ.

So, what about this parameter in STM32F3? How manny cycles cost before main process be suspended/halted? (or said how many cycles from edge to IRQ?)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-05 4:10 AM

> interrupt and DMA use same trigger edge from external.

How does the external signal trigger DMA? EXTI can't directly trigger DMA. Through a timer capture channel?

> How manny cycles cost before main process be suspended/halted?

The main process is stopped immediately after finishing the currently executed instruction, so within 2 cycles. Even multiple-store instructions will be stopped, and resumed after the interrupt finished. This can be disabled somewhere, but you would know if you did that.

During the 12 cycles interrupt latency the MCU is not executing instructions, but it is busy pushing registers to the stack.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-05 6:13 AM

Thanks berendi,

> How does the external signal trigger DMA? EXTI can't directly trigger DMA. Through a timer capture channel?

Yes, the exti pin also is configured as timer ETP pin, trigger UEV by edge and send a DMA request same time.

From the edge to DMA transfer trigger, it's two clocks need(Timer works as system frequency):

And with another 2 clock for DMA arbitration, the DMA will read data at next clock. so, there will be 2 + 2 = 4 clocks from edge to DMA read data. I have to make sure CPU is suspended at 5th clock(I could add external trigger filter argmuments to increase the detection clock).

> The main process is stopped immediately after finishing the currently executed instruction, so within 2 cycles.

There will be a synchronization time(or detection time) from edge to suspend CPU, but I think it's not for finishing the currently executed instruction, but for edge detection and NVIC, 2 cycles maybe right, but I need a exactly right number for security.

I tested 14 to 16 cycles from edge to the head of first interrupt instruction execution(Run in CCM RAM), told me that 2 to 4 cycles maybe are the result, but it don't match fixed 2 cycles, make me confused, so wanna figure out the real cost in theory.

Is there a document show the detail when EXTI to IRQ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-05 7:00 AM

> Is there a document show the detail when EXTI to IRQ?

I haven't found, but it doesn't mean that there is none. EXTI reaction could be delayed by 1 to 3 cycles as well, bit I don't have any definitive source on this.

> I tested 14 to 16 cycles from edge to the head of first interrupt instruction execution(Run in CCM RAM), told me that 2 to 4 cycles maybe are the result, but it don't match fixed 2 cycles, make me confused, so wanna figure out the real cost in theory.

The external trigger could come just a nanosecond before or after the system clock edge, and after 2 cycles of propagating through EXTI, it could hit either a 1-cycle or 2-cycles instruction. But this is speculation too.

You can of course increase the DMA delay to a safe value, either through the trigger filter, or setting the timer in one pulse mode, slave mode: trigger mode. The timer would count up from 0 to ARR and then trigger DMA. So you can set any delay in ARR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-05 8:02 AM

Really appreciate your reply, thank you berendi, I will increase DMA delay with a secure clocks before some official explanation.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-05 8:58 AM

The 12 cycle latency requires that there are no wait-states, either explicit or implicit, in the memory system.

http://infocenter.arm.com/help/index.jsp?topic=/com.arm.doc.faqs/ka16366.html

Also, EXTI in 'F3 is on APB2, and I wouldn't be surprised if there would be an additional synchronization delay between EXTI and processor/NVIC, possibly dependent on APB2 prescaler (potentially causing jitter in the latency).

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-05 9:02 AM

You are right, but the edge to interrupt needs propagation through edge detector/NVIC, that will cost extra cycles.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-04-05 10:16 AM

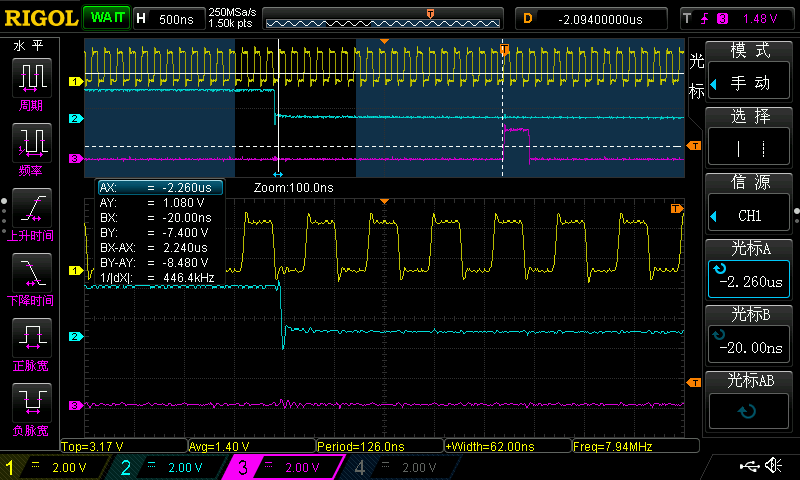

After I reuce Core clock to 8Mhz and test, I get constant about 18 cycles(2 exti propagation + 12 interrupt store + 4 insturction cycle)

Channel 1: MCO, clock output

Channel 2: Btn, detect on falling edge

Channel 3: GPIO, set in EXTI interrupt routine

I think my previous error was caused by MISMEASUREMENT, it was much easier at low frequency.

Anyway, thank you.

- Synchronizing PWM Signal through an external Signal in STM32CubeIDE (MCUs)

- ADC in DMA circular mode with LL Library Problems in STM32 MCUs Embedded software

- STM32 SDRAM Access Results In HardFault in STM32 MCUs Products

- Achieving the theoretical ADC Conversion Time (12-bit) on STM32G4 in STM32 MCUs Products

- Bug in TIM_Base_SetConfig, fix TIM_Base_SetConfig to block first interrupt in STM32 MCUs Embedded software