- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: FMC synchronous PSRAM - lost AHB transactions

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

FMC synchronous PSRAM - lost AHB transactions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 06:09 AM

Hello

I have FPGA with memory mapped peripheral what I would like to control from external STM32 MCU (STM32F767 ). I chose FMC peripheral in synchronous PSRAM mode because communication can be easily implemented in HDL wrapper. I was inexperienced in this stuff so firstly I just connected logic analyzers to FMC bus, made some configuration and did some write accesses 'into air'.

Unfortunately I have faced some problems what I don't understand.

My configuration for all PSRAM banks:

DataAddressMultiplex = off;

MemoryType = PSRAM; MemoryDataWidth = 16b; BurstAccessMode = onWriteBurst = on;

Wait signal manage = off WriteOperation = on; ExtendedMode = None ContinuousClock = on WriteFifo = on; PageSize = none;Timing:

AddressSetupTime = 15; AddressHoldTime = 15; DataSetupTime = 255; BusTurnAroundDuration = 15; CLKDivision = 2; DataLatency = 2; AccessMode = MODE_A;First problem is that I'm loosing some AHB requests.

Example code

#define ADDR_PSRAM10x60000000 //PSRAM Bank 1

uint32_t wdata[8] = { 0x00010000, 0x00030002, 0x00050004, 0x00070006,

0x00090008, 0x000B000A, 0x000D000C, 0x000F000E };

uint32_t *pAddr = (uint32_t*) ADDR_PSRAM1;

for (i = 0; i < 8; ++i) {

*pAddr++ = wdata[i];

//myDelay();

}I would expect that I will see 8 FMC write transactions but I saw only first one (sometimes two transactions). I was adding some sw delay (commented myDelay()) which solved the problem but I dont think it's good aproach.

First I had CLKDivision 16 so I though that CPU is too fast for FMC, so I switched division to 2 without noticeable effect.

Am I doing something wrong? I suppose FMC peripheral is for FLASH/RAM extension of MCU memory so there should be no problem. Is there some bit where I can check that FMC transactions is done? In reference manual there is information about AHB error flag but it is not useful for me.

Second problem is OCCASIONAL '

leakage

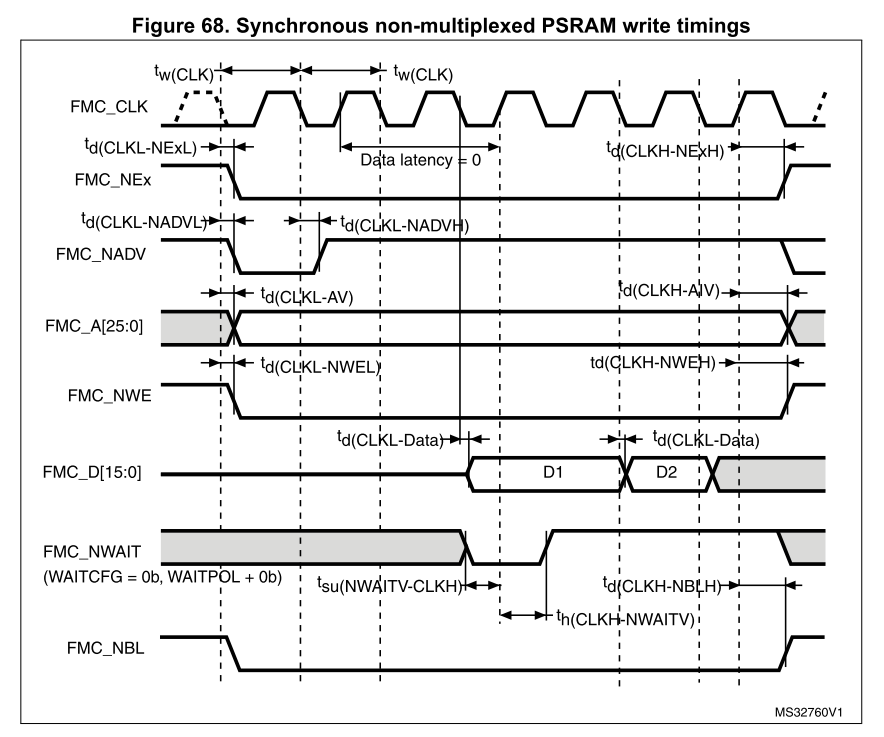

' in FMC transaction from following AHB data 'stream'. Please see attached pictures (1.png - 6.png). Pictures are screenshots of FMC entries from logic analyzer (see code above).You can see values of D0-D7, A0-A4, NE1, NADV a CLK signals in FMC transactions. NE1 is basically same as NWE signal. Cursor 'C1.2' points at rising edge of clock where low 16b data from 32b value is written. Following rising edge should be remaining high 16b part.

After that NWE/NEx signal should be deasserted acording to reference datasheet but not in my case. You can see in first two pictures (1.png, 2.png) that two 32b AHB transactions were done in one FMC write. Sometimes I observed 3x32b in one FMC operation. Remaining FMC entries are ok from my point of view - values from 0x00090008 to 0x000F000E are written correctly.

This problem doesn't happen when write FIFO is disabled, but I don't know why...I have found nothing about it in reference manual.

Can someone please help me?

Regards

Daniel

#psram #ahb #fmc- Labels:

-

FMC-FSMC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 06:23 AM

And where's that WR signal?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 06:35 AM

I wrote 'NE1 is basically same as NWE signal'.

NWE=WR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 06:54 AM

It has the same waveform as NE (enable chip).

NWE is asserted when write operation is done.

Just see Figure 68. Synchronous non-multiplexed PSRAM write timings

In my opinion there is error in Data latency value - it should be 2

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 07:46 AM

OK but I don't see it on the waveforms.

Or did you connect the NWR signal to NE?

Or just you observed it in some separate way and found it to have the same waveform?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 07:53 AM

OTOH, NADV pulsing in non-multiplexed mode is suspicious, too.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 08:18 AM

I've seen the waveforms in RM/DS, but the FMC is quirky and badly documented in details, so it's not out of interest to see the actual behaviour. Did you try exactly those settings from the table in RM?

You may perhaps want to start from the asynchronous case. I'd also recommend to avoid intermediate 'layers' and work directly with the registers - there are only 2 (3) of them.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 08:30 AM

Yeah, for initialization I´m using LL library stm32f7xx_ll_fmc.h. It's written decently so I will rather make some review of code and make check of values written into registers.

I would like to avoid of usage asynchronous mode

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-30 08:46 AM

I would like to avoid of usage asynchronous mode

I understand that. My point is, that using a known working mode could eliminate possible gotchas outside FMC.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-10-31 06:27 AM

My colleague successfully use PSRAM mode on STM32F407.

There is not so much difference between FSMC (F4) and FMC (F7). I only use continuous clock feature.

The point is that FMC SHOULD be blocking for write/read accesses but obviously it is not my case. I can only block CPU when NWAIT is enabled and in active state. It has to be problem somewhere else (cache, AHB...)

- STM32U5A5: PSRAM (4MB external RAM) via QSPI (OCTOSPI1) - for you in STM32 MCUs Products

- Synchronous mode for DMAMUX - Trigger via EXTI in STM32 MCUs Boards and hardware tools

- In STM32F103xx manual, FSMC timing is seem wrong in STM32 MCUs Products

- STM32CubeMX 6.1.0 released in STM32CubeMX (MCUs)

- AUDIO RECORD - MEMS > DFSDM > I2S > FATFS > Ethernet in STM32 MCUs Embedded software