- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Do HRTIM faults respect configured deadtime?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Do HRTIM faults respect configured deadtime?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-15 12:50 PM

Hi

Assume that i set up an H-bridge and and control it via the HRTIM block and use the build in deadtime features. I then also enable a couple of faults. The bridges safe state will be to set both lower transistors to be OFF and the two upper once to be off. I then run the H-bridge in a PSFB mode.

Now all of a suddenly a fault is triggered while the bridge is conducting. Lets say that "top left" and "bottom right" transistor is enabled. Transition to safe state will cause the mcu turn off "top left" and turn on "bottom left" but will it respect the configured deadtime while preforming this transition or will it change both outputs simultaniously and risk a left side shoot thru on the H-bridge

Best regards

Martin

- Labels:

-

HRTIM

-

STM32G4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-27 01:20 AM

Hello Martin @DreamOnDirac

According to the Reference Manual, "Once a fault has been triggered, the outputs take a predefined safe

state. This state is maintained until the output is re-enabled by software.". There is no deadtime when a fault occurs, all outputs are forced to the low level in case of FAULT event.

Here is some documentation, the RM(~ page 919) and the AN4539(~ page 27).

Best Regards,

Pierre

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-01 01:23 PM - edited 2023-10-03 06:15 AM

How sure are you on this?

I discovered this presentation:

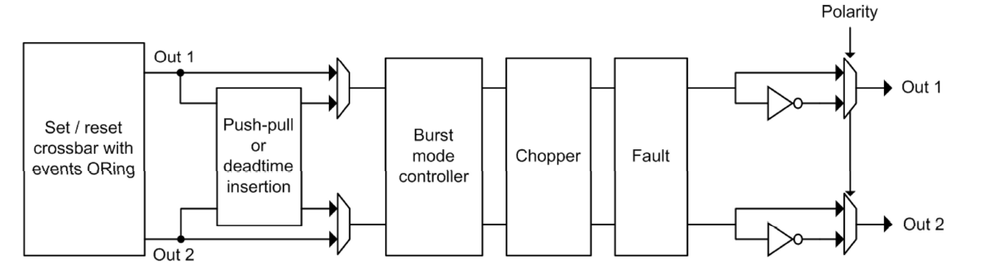

And looking at page 36. There appear to be a dead time insertion on fault.

Or is this related to "Burst mode delayed entry" and the DIDL bits. If this could be used without actually using the burst mode controller, that might acheive want I want.

Regards

Martin

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-02 08:15 AM - edited 2023-10-03 06:16 AM

(Deleted by author)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-03 09:05 AM

Hello Martin @DreamOnDirac,

- After a fault is triggered, outputs go into predefined safe states without any deadtime. It's an emergency procedure and we can see in the schema under that fault stage is directly close to the output to go faster. We even care about the impact of the filtering option on faults they can introduces a slight delay on the state outputs.

- For your application, you can also check the 27.3.10 Delayed protection chapter in the STM32G4 RM. It's a specific protection schemes when it is necessary to shut down the PWM outputs in a delayed manner.

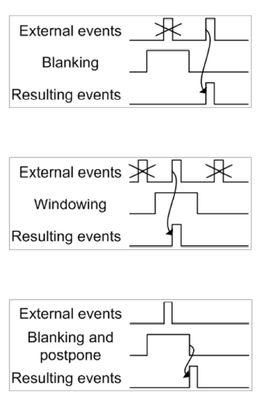

- Did you consider the blanking or windowing mode ? In fact, we can have a quite similar behavior by conditioning faults signals.

Best Regards,

Pierre

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-06 07:23 AM

Hi

If anyone else finds this thread.

I did not succeed in using hardware to fix this. Instead i made sure that any faults made sure that the entire H-bridge was drawn low and I then set the HRTIM FLT interrupt to be the highest priority in the system:

Inside the ISR I turned on the bottom transistors again. This gave me a "deadtime" to the deenergize state of around 550 ns which is not ideal, but a lot better than what i used to have.

Regards

Martin

- How to Properly Configure and Trigger a Soft Break on TIM1 in STM32 in STM32 MCUs Motor control

- STM32G0 minimum ADC frequency in STM32CubeMX (MCUs)

- SPI communication issue on STM32F103RB (sort of buffer over/underun) in STM32 MCUs Embedded software

- STM32G431 SPI Strange Data in STM32 MCUs Products

- HRTIM: won't trigger regular channel ADC in STM32 MCUs Products