- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: DMA: ST Vs NXP

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

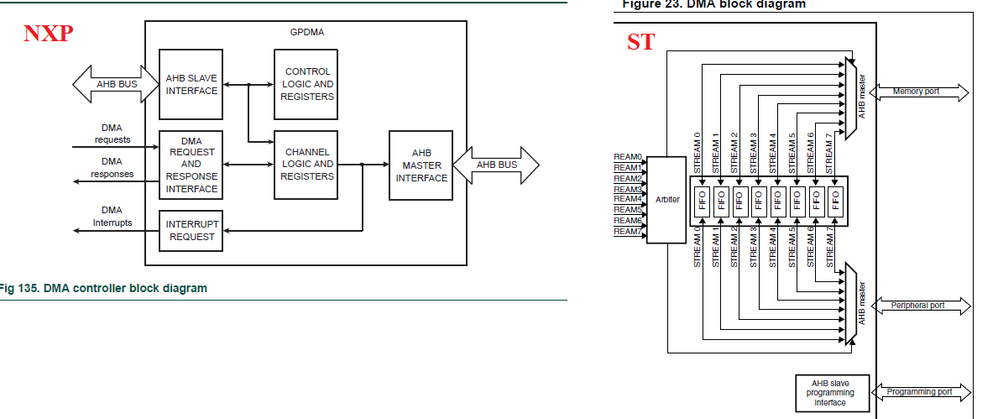

DMA: ST Vs NXP

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-04 11:27 PM

Hello I work both on NXP and ST MCUs

In DMA i saw ST has 2 AHB master Ports and NXP has got only 1 .

Why such design ? which is more beneficial ?

for example if want to do P2M then 2 master ports are really needed or can be done with only 1 as in NXP ?

Thanks.

#nucleo-stm #stm32f4- Labels:

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-05 12:36 AM

In STM32, there are two different DMA modules: a single-port in 'F1, 'F3, 'F0, 'L0, 'L1 and 'L4; and the dual-port if 'F4 and 'F7/H7.

The benefit of dual-port design, together with the dual-port AHB-to-APB bridge is, that the AHB bus where the peripheral lies is not blocked by the DMA transfer; and vice versa, different channels (here called streams) in the DMA controller can simultaneously access the different ports (read: they work simultaneously).

Drawback is the increased complexity thus larger occupied silicon area and potential for designer errors.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-05 05:48 AM

Thanks for the reply and i didnt understand it though . Sorry !. But are you saying that 2 streams in ST can work simultaneously ? like can i use one stream for P1 to sram1 and another stream for P2 to SRAM2 ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-05 07:23 AM

Eight streams in both DMA controllers can be concurrently active, prioritization dictates who take their turn first, and presumably you're not driving things into saturation, where contention strangles the system performance. ie desired bandwidth exceeds available bandwidth

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-07 05:08 AM

Hello

n.serina

,You may refer to thechapter 'System performance considerations' in the

Application notedescribes how to use DMA controller in STM32F2, STM32F4 and STM32F7 Series,Best Regards,

Imen.

Thanks

Imen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-07 10:33 PM

Thanks Clive. in STF0x ST documentation uses 'channels' in F4 'streams' . i am quite confused by this. are channels and streams same ? in F4, data is loaded from src to internal fifo of the DMA controller , but F0x DMA does not seem to have FIFO. So in F0x where packing/un-packing happens ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-02-08 07:05 AM

are channels and streams same

In the dual-port DMA, 'streams' are the same as 'channels' in the single-port DMA; whereas 'channels' denote the selection of trigger which in those DMA happens in the control register (which in single-port DMA is handled differently, either through a simple OR (e.g. in 'F3) or through a separate selector register in DMA).

So in F0x where packing/un-packing happens ?

There is no packing/unpacking in the single-port DMA (e.g. in F0). Depending of whether source is narrower or wider than destination, data are truncated or zero-expanded. Read the DMA chapters in RM for the details.

JW

- old version of IDE in STM32CubeIDE (MCUs)

- STM32H753 SVD File FDCAN Discrepencies in STM32 MCUs Products

- Warning The provisioning scripts are only supported for DK boards in STM32CubeMX (MCUs)

- STM32U575RGT6 without UCPD in STM32 MCUs Products

- STM32H723: Can't connect to bootloader via UART / at all in STM32 MCUs Products