- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Clock cycle shift on GPIO output STM32F103

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Clock cycle shift on GPIO output STM32F103

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-11 09:49 PM

Dear Community,

I am porting an old application made on AVR to STM32, and I am facing a strange timing issue.

In a nutshell, the application is reading sector (512 Bytes) from a SDCARD and output the content of the buffer to GPIO with 4us cycle (meaning 3us low, 1 us data signal).

The SDCard read is working fine, and I have written a small assembly code to output GPIO signal with precise MCU cycle counting.

Using DWT on the debugger, it give a very stable and precise counting (288 cycles for a total of 4us).

When using a Logic analyser with 24 MHz freq, I can see shift of signal by 1 or 2 cpu cycles and so delay.

I have tried to use ODR directly and BSRR but with no luck.

Attached :

- Screenshot of the logic analyzer

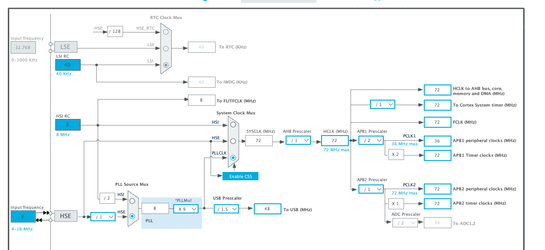

Clock configuration

Port configuration:

I do not know where to look at to be honnest

- Labels:

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-13 05:02 AM

I will try the DMA + SRAM and maybe checking interrupt as well

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-13 05:09 AM

This is the view NVIC in CubeMX,

Does it change something to uncheck these ?

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-13 05:55 AM

@vbesson wrote:Yes this is my goal, I have done it with the ATMEGA328P but the SPI speed does not allow accurate writing,

...

I do not get your point with USART in synchronous or SPI ? you mean having a SPI to DMA and then DMA to USART ?

...

No, the idea is to use a timer to generate the clock you need and use that timer signal to clock either a USART in synchronous mode (using the TX signal as your data) or a SPI in Slave mode (using the MISO signal as your data). Either approach takes care of sending data bits based on your clocking. At this point you can add the circular double-buffer DMA mechanism to feed the data bytes to the USART or SPI.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-13 12:06 PM

This is getting really embarrassing ... ;)

Putting DMA in motion, I have better accuracy but stil some glitch... this is crazy... really really crazy

I do not understand...

V

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-13 12:07 PM

Frame should all be 1us High and 3us low, and I still have glitches...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-13 01:30 PM - edited 2024-05-13 01:35 PM

I don't see any glitches in your screenshot.

Timing also looks good. The imperfections be an issue with synchronization between the logic analyzer and the microcontroller. Try a logic analyzer with a higher clock and you might see even better timing. Clock dither of the MCU and/or the logic analyzer can also be a factor. Rise time can also be a factor in imperfect measuring of pulse widths.

You say your logic analyzer is clocked at 24MHz, but that would make 3.063us about 73.512 clock cycles of your logic analyzer (or exactly 73.5 cycles and the 3.063 is a rounded number). So that cannot be correct. Does it sample at both edges of the clock? So 48 MSamples/second?

Click "Accept as Solution" if a reply solved your problem. If no solution was posted please answer with your own.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-13 09:27 PM

I have done sampling at different logic analyser speed rate and the pulse timing is not right. I have a comparison with an ATMEGA328P.

The issue is that I have 402 bytes per data stream to be sent, it means 402*8*4 us period = 12 864 us for a data sector.

When I have 0.063 us shift time to time, I can have more than 1 bit or 2 shift in the end and data corruption with the 2 byte XOR CRC send at the end of the transfer.

I found an interesting article, and I am currently testing it Disabling / enabling IRQ on STM32 for atomic read

Will keep you posted

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-14 02:03 AM

Use logic analyzer or oscilloscope with much higher sampling frequency then your MCU frequency or you will not be able to distinguish measurment relics from real MCU output jitter. Imagine that you generating perfect square wave with frequency 72MHz/20=7.2MHz (period 277.8ns). If you sample this signal by analyzer with 24MHz (period 41.67ns) the you will see jittering output of 2 consecutive periods in duration 6*41.67 (250ns) and one period in duration 7*41.67 (292ns) - on perfect square wave ! And that can leads you to wrong conclusion that jitter comes from MCU output ...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-14 02:07 AM

Hello Michal,

Thanks and I genuinely agree with you. However it is not easy to find an AL with capability above 24 MHz.

what I do is to look at the data stream over the whole transmission period and I should not get significant delay. Unfortunately I have delay and not a 250kHz fdata freq.

Vincent

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-14 03:32 AM

Ordinary oscilloscope should be able to handle it with ease. As others have already written - use SPI or USART or Timer + DMA and you will get easy seamless pulse stream and with minimal CPU load.

- HRTIM PWM transients greater than a period in STM32 MCUs Products

- synching HRTIM's TIMA and TIMB in STM32 MCUs Products

- DAC Sine Wave & Vertical Shift in STM32 MCUs Products

- Comparator Bug Report on STM32G0 in STM32 MCUs Products

- No I2C communication with Nucleo-F411RE and ADXL345 in STM32 MCUs Boards and hardware tools