- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: BDMA 50ns offset between Clock (LPTIM2 PWM) an...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

BDMA 50ns offset between Clock (LPTIM2 PWM) and 16bit GPIOE.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-07 07:01 AM

Hi all,

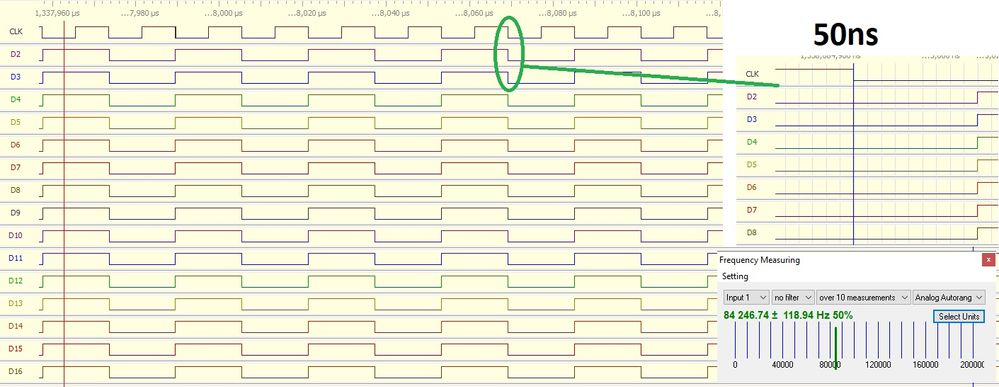

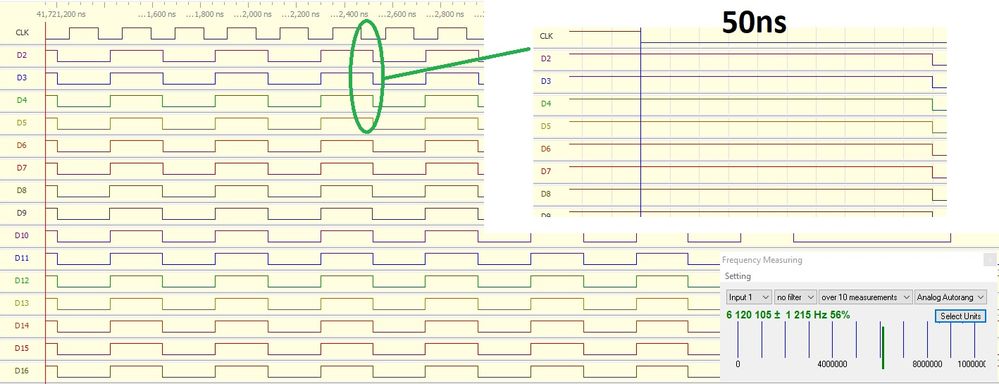

I working on parallel synchronous transmission. I am using LPTIM2 as clock (PWM) and GPIOE as data bus. It is working with BDMA but here is 50ns offset between Clock and data no matter what frequency I setup. Please see pictures below 84kHz and 8MHz. So I would like to eliminate 50ns offset between clock and data.

I trying to make synchronisation at falling edge of CLK. And my goal is reach 16MHz.

It is even possible with STM32H7 ?

Current configuration STM32H743, 400MHz, SW4STM32, HAL

Thank you

Michal

- Labels:

-

GPIO-EXTI

-

LPTIM

-

STM32H7 Series

-

SW4STM32

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-07 10:06 AM

Is this a timer-triggered DMA from memory to GPIO?

Surely, there's some propagation/resynchronization time from timer to DMAMUX, within DMAMUX, from DMAMUX to BDMA; then BDMA performs arbitrration, loads the value from the source memory and finally outputs to the GPIO, again all these processes take some time to accomplish.

You can compensate somewhat by triggering the BDMA from a different channel of the timer, slightly skewed to the one which outputs the "clock".

Note, that in a real program, not only a fixed delay is imposed, but due to potential conflicts within BDMA and on the source/destination buses of the DMA, this time might be increased at certain moments, resulting in jitter.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-08 04:42 AM

Yes a timer-triggered BDMA from memory SRAM4 to GPIO

Sure I understand that all these operation take some time, however the example AN4666 with STM32F4 and STM32L4 work without resynchronization.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-10-08 07:31 AM

And what is chapter 1.2.2 Data and clock alignment consideration talking about, then?

JW

- PWM center aligned to half-period of TIM in STM32 MCUs Products

- STM32U5 OPAMP usage with sine wave with voltage offset in STM32 MCUs Boards and hardware tools

- Firmware Update on STM32L4S9ZITx with bootloader and dual bank firmware in STM32 MCUs Embedded software

- OpenBootLoader Advice / Best Practice in STM32 MCUs Embedded software

- STM32WL3x LBT example in STM32 MCUs Wireless