ADC only 4Msps?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 12:03 AM

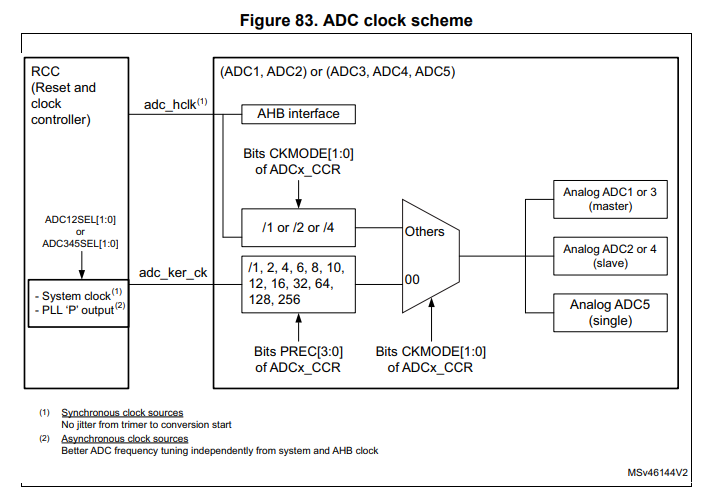

Documentation say ADC have max 4Msps, but it refer olways to 60MHz to adc (60MHz * 15 cycle = 4Msps) but manual say ADC max frequency is 170MHz, then 170MHz * 15cycle = 11Msps.

This clock is different from Fadc (aka adc kernel clock)?

Documentation 7.2.11 ADC clock

- Labels:

-

ADC

-

STM32G4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 3:23 AM

Read RM0440 21.4.3 ADC clocks but the interface clock and the clock used for the ADC.

170 MHz is only the interface clock!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 3:30 AM

then what is source of adc kernel clock? and what prescaler register it or have some default prescaler (and adc kernel clock is depend on sysclock?)?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 8:43 AM

I read RM0440 21.4.3 and I know AHB bus could have different clock that ADC clock, but still 7.2.11 say about ADC clk not AHB bus.

"Alternatively, the ADC clock can be derived from the AHB clock of the ADC bus interface", then it could have same clock that interface?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 10:25 AM

if PLL 'P" and SYSCLK is only for source interface clock, then where is source clock for ADC conversion?!

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 12:06 PM

You're expected to select a clock and prescalers to have the clock at the mux to be 60 MHz or less.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-03 9:23 PM

well if the spec gives msps probably there is an analog limit more than digital clocking one. dig the adc electrical spec in datasheet

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-07-04 12:03 AM

Thanks for answer. In https://www.st.com/resource/en/datasheet/stm32g474cb.pdf we have ADC characteristics and there is lmitation. Then there is problem with samples... examples from cube firmware packet have set ADC clock to 170MHz and it work, however it could have different precision and generate EMC issue.

ST should fix their examples to correct ADC clock value.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-09-15 8:52 AM

Hi all,

I'm back about this problem. There is possibility to clock ADC with 170MHz clock and run over 4Msps (I run it with 8Msps). Of course documentation say I shouldn't do it, but in examples you (I mean ST) provide ADC clk is set to 170MHz!!! and in cubeMX there isn't any warning that say user exceeds ADC clock value!

I just watch Biricha materials and they use soft generated from cubeMX with probably 170MHz ADC clk and all work great...