- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: ADC Noise

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

ADC Noise

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-13 3:55 AM - edited 2023-11-13 3:57 AM

We use a STM32F7xx microcontroller with LQFP144 case

Part of the ADC Pins are on the 1-36 pin side.

Unfortunately this is also the side where the Quartz (Pins OSC_IN and OUT, PC14-OSC32_IN, PC15-OSC32_OUT) and the RMII_CLK are mapped.

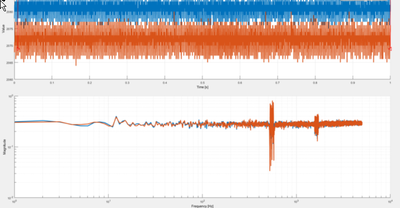

This leads to additional noise (app. 10 LSB with peak regions at 500 Hz compared to 5 LSB noise on other similar filtered sensor signals) on the pins 36 (ADC123_IN2) and 37 (ADC123_IN3) despite anti-aliasing filter.

Unfortunately we could not find any other pin available on ADC1 and ADC2.

Is this a well known problem that oscillators may disturb ADC's of STM32Fxxx microcontrollers?

- Labels:

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-13 6:53 AM

Hi @gviereck ,

In the errata sheet ES0290, we recognize that some internal noise may impacting the ADC accuracy and 2 workaround options are suggested.

I invite you to review this errata and apply the workarounds then to let us know the results. To enhance the ADC accuracy, don't forget the AN4073 as well.

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-14 2:29 AM - edited 2023-11-14 2:37 AM

Hello Amel,

Thanks very much for having answered so quickly.

The annoying additional noise is not a general issue for all ADC pins.

We have 6 sensor signals connected to ADC Pins.

2 of them show additional noise.

They are connected to PA2 (Pin 36 of STM32F756ZG in LQFP-144 case) = ADC123_IN2 and PA3 (Pin Nr 36).

PB0 = Pin 46 = ADC12_IN8 gave better results

but PC0 = Pin 26 = ADC123_IN10 or PC2 = Pin 26 = ADC123_IN12 gave no better results.

Is this worth trying PC1 or PC3 = Pin 29, too ?

Layout does not seem to be the problem but more to which ADC pin the sensor signal is connected.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-14 3:50 AM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-14 4:30 AM

Yes.

I measured the noise without anything connected to the input stage composed of anti-aliasing filter and voltage adaption circuit.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-14 5:22 AM - edited 2023-11-14 8:13 AM

Hi @gviereck

It seems your issue is related to the cross talk phenomena. Please refer to the AN2834 "How to optimize the ADC accuracy in the STM32 MCUs" / section 3.2.11 I/O pin crosstalk.

Solution in the section: 4.2.11 Minimizing I/O pin crosstalk

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-14 9:33 AM

Thanks for you contribution.

I wish, you were right.

But the fact is that the sensor tracks do not cross or go along high speed signals.

Moreover, we have a several layer PCB among which are analog and digital ground planes and supplied voltage (e.g. +3.3V power-supply planes).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-14 10:03 AM - edited 2023-11-14 10:17 AM

1. pin36/37 are not close/next to osz.

ed. sorry, i thought on H7... 16bit. so on F7xx 12bit adc is a little bit more - about 8mV.

2. 10LSB at 16 bit adc here (ref. 3v3) is about 0,5mV . so to see, what the adc is doing, solder short wire from pin36 to pin31 and cut any >10mm long trace at pin36. THEN you can see, is the reason stray cap/induced spikes or bad chip multiplexer or whatever on chip. And dont forget, to keep the nearby pins "quiet", not switching. Also switching pins on same port mux may produce spikes, if port speed is high (set all ports here to low speed) or high speed signal is coming in there , producing some ringing/overshoot, and some mV spikes are here (via the internal protection circuit/diodes).

3. try with different sampling time (i found best results at 8.5cycles - ymmv); these adc are real fast in the sample/hold inputs, even stray in at 2,4Ghz (wifi or mobile net...) producing effects in 10...20LSB range, or more.

So try with some screen, if possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-15 12:40 AM - edited 2023-11-15 12:42 AM

Hello AScha.3,

Thanks for your contribution that makes sense.

Some more details about our HW and FW implementation:

1) STM32F756 has 3 ADC's with 12bit resolution.

=> 1 LSB corresponds then to 0.8 mV

2) Within our actual FW the sampling frequency is 10 kHz per channel.

3) The LQFP-144 case is a square form.

The side with pin nr's 1-36 receive the 2 quartz (CPU main clock and RTC Clock) and outputs the RMII clock for Ethernet connection.

4) The 2 (more) noisy ADC inputs are also on this side.

5) PA2 = ADC123_IN2 = Pin nr 36 is next to PA1 = RMII_CLK

6) Connection distance between last filter stage and PA3 = Pin nr 37 is very short (3.3 mm) and is crossing nor getting along no other signal.

6) DSP law: When aliasing occurs the digitalized signal is unrecoverable

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-15 1:03 AM

ok, so for a test: i would disable the RMII clk, this is hi speed and may be the source of some cap. stray in.

and next : the test with a short wire to vssa . (if still "unusual" noise there)

just guessing: rmii clk at pin 35 and adc-in at pin 36 - only a ground trace between the pins could (!) reduce cap. coupling as some screen; better not use a pin so close to a RF clock or similar hi speed signal.

- I2S Microphone Output Problems in STM32 MCUs Products

- How to disable XSPI SCK Clock preamble? in STM32 MCUs Products

- LTDC Test with External Flash on STM32H730 – Issues with Noise and Distortion in STM32 MCUs Products

- STM32H747I-DISCO, codec outputs noise in BSP example. in STM32 MCUs Embedded software

- Trying to make sense of the audio system on the STM32F407-g Discovery board: in STM32 MCUs Boards and hardware tools