Turn on suggestions

Auto-suggest helps you quickly narrow down your search results by suggesting possible matches as you type.

Showing results for

- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Embedded software

- Re: Potential Bug in STM32Cube SPI routine

Options

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Potential Bug in STM32Cube SPI routine

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-06-05 10:15 AM

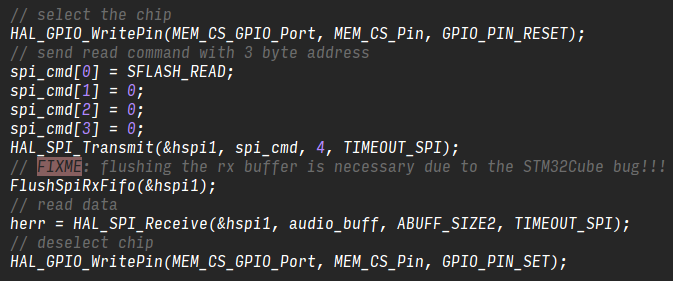

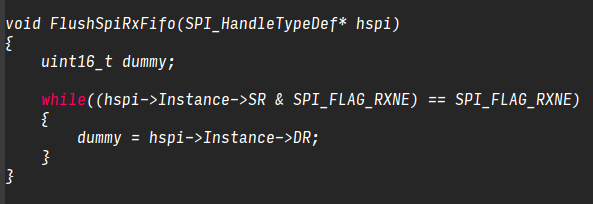

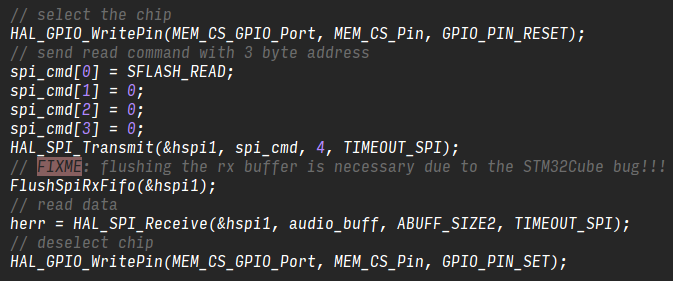

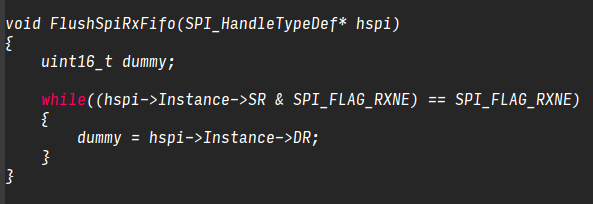

Posted on June 05, 2016 at 19:15 The problem of this code is that the HAL_SPI_Transmit() leaves data on the RX buffer by default, so that when HAL_SPI_Receive() was executed, 3 bytes of garbage data was introduced at the beginning of the read buffer while the same amount of data was missing at the end.So, I have to flush the Rx buffer before every HAL_SPI_Receive() call.

The problem of this code is that the HAL_SPI_Transmit() leaves data on the RX buffer by default, so that when HAL_SPI_Receive() was executed, 3 bytes of garbage data was introduced at the beginning of the read buffer while the same amount of data was missing at the end.So, I have to flush the Rx buffer before every HAL_SPI_Receive() call. where

where Thanks, #stm32cube #spi #bug

Thanks, #stm32cube #spi #bug

Hello,

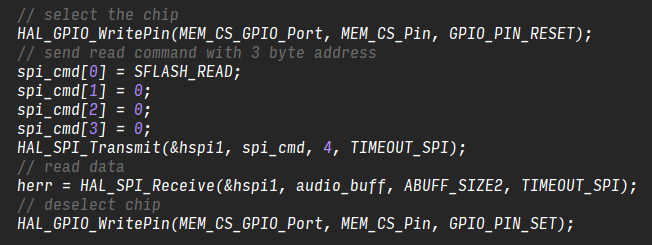

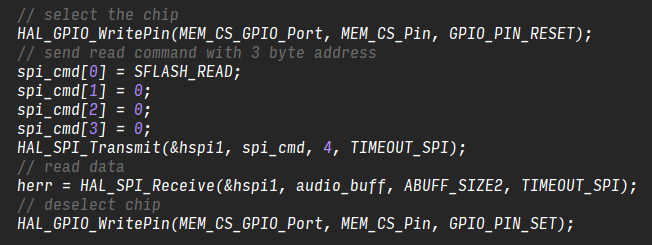

In my senario, a SPI eeprom is connected to a STM32F051, whose SPI module was set to a full duplex master mode. My original code to read a block of data from the eeprom was like this: The problem of this code is that the HAL_SPI_Transmit() leaves data on the RX buffer by default, so that when HAL_SPI_Receive() was executed, 3 bytes of garbage data was introduced at the beginning of the read buffer while the same amount of data was missing at the end.So, I have to flush the Rx buffer before every HAL_SPI_Receive() call.

The problem of this code is that the HAL_SPI_Transmit() leaves data on the RX buffer by default, so that when HAL_SPI_Receive() was executed, 3 bytes of garbage data was introduced at the beginning of the read buffer while the same amount of data was missing at the end.So, I have to flush the Rx buffer before every HAL_SPI_Receive() call. where

where Thanks, #stm32cube #spi #bug

Thanks, #stm32cube #spi #bug

Labels:

- Labels:

-

Bug-report

-

SPI

-

STM32Cube MCU Packages

3 REPLIES 3

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-06-08 6:24 AM

Posted on June 08, 2016 at 15:24

Hi lee.sungjune.001,

If the SPI is transmitter, the RXFIFO shouldn't be used.I don't think that the root cause of your problem is the function HAL_SPI_Transmit.You need to more investigate how the 3 bytes remain there.-Mayla-To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-06-08 7:59 AM

Posted on June 08, 2016 at 16:59

Hi Mayla,

Thanks for the reply. However my understanding is that when SPI is set to full-duplex mode, the RX buffer is always operational regardless of HAL_SPI_Transmit() or HAL_SPI_TransmitReceive() being used.The problem in my case is that the RX buffer was not empty when HAL_SPI_Receive() was called but had un-read garbage data due to previous full-duplex transaction in this case HAL_SPI_Transmit().One obvious solution is not to use HAL_SPI_Transmit() / HAL_SPI_Receive() in full-duplex mode but use HAL_SPI_TransmitReceive() only. But the situation is the same actually since you have to separate your data from the RX buffer whose contents include garbage bytes at the beginning. Thanks,Options

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-06-08 3:01 PM

Posted on June 09, 2016 at 00:01

In SPI full-duplex mode transmission and reception are synchronous. When master is sending data on MOSI line along with clocks on CLK line, it is also receiving data on MISO line.

I am not familiar with these two HAL functions, but you definitely should not call them separately.When I want to start data transfer (and receive data from slave), I first set RXDMAEN bit in SPI->CR2 register. Thus, SPI master is ready to receive data. After that I set TXDMAEN bit in SPI->CR2 register. Now, master starts to send data out along with clocks. It is receiving at the same time. (Note: SPI and both DMA channels (Rx, Tx) should be already enabled when setting RXDMAEN and TXDMAEN bits.)When TCIF for Tx in DMA registers is set, all data were sent out. At that point master stops sending clocks too. If amount of data which should be received is equal to amount of data that was transferred, TCIF for Rx in DMA registers is set too.Then you should have all data in your RX buffer.

Related Content

- Greenhouse Temperature Controller - STM32H750BDK in STM32 MCUs Products

- help debug corrupted memory location in STM32 MCUs Embedded software

- Help building from STM32CubeF3 in STM32 MCUs Embedded software

- After updating the slot size MCUboot gives error for secondary slot image invalid for FOTA in STM32 MCUs Embedded software

- MCUBOOT bootloader upgrade OTA in STM32 MCUs Products