- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Boards and hardware tools

- Re: minimum wiring STM32F446

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

minimum wiring STM32F446

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-30 01:32 PM

Hi,

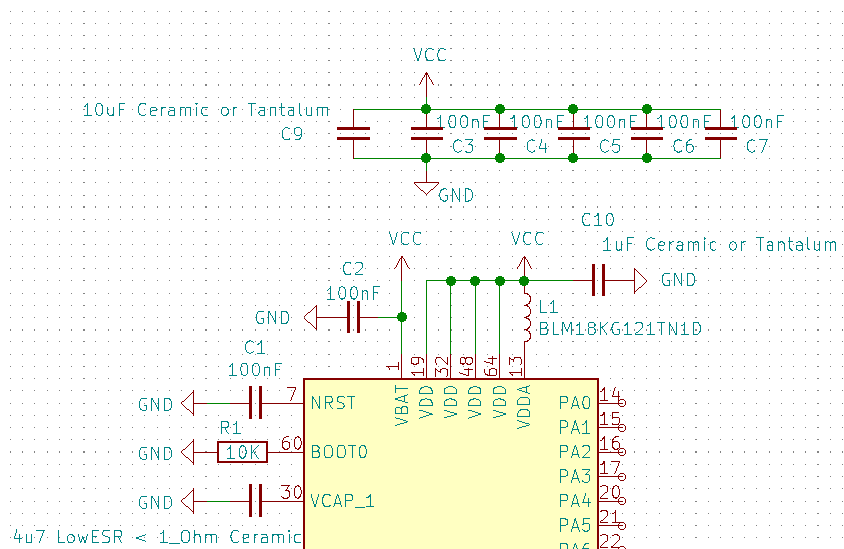

i want to know if i did the wiring correct?

The 4 x 100nF will be connected close to PIN 19, 32, 48 and 64.

PIN 1 got a 1uF.

On PIN 13 (VDDA) i added a bead as well.

NRST will not be used in the final application, is the 100nF anyway needed?

BOOT0 is grounded by 10k.

VSS is directly connected to ground. In the Nucleo Board description i saw that PIN 31 and PIN 47 could be connected to a 2.2uF, does someone know why? There is a solder bridge.

Solved! Go to Solution.

- Labels:

-

STM32F4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-21 01:56 AM

Hello,

1) On the pcb, where is the right place to put that cap? Are there any recomendations?

AN4488:

"8.3 Power supply decoupling

All power supply and ground pins must be properly connected to the power supplies. These

connections, including pads, tracks and vias should have as low impedance as possible.

This is typically achieved with thick track widths and, preferably, the use of dedicated power

supply planes in multilayer PCBs.

In addition, each power supply pair should be decoupled with filtering Ceramic capacitors

(100 nF) and one single Tantalum or Ceramic capacitor (min. 4.7 µF typ.10 µF) connected in

parallel. These capacitors need to be placed as close as possible to, or below, the

appropriate pins on the underside of the PCB. Typical values are 10 nF to 100 nF, but exact

values depend on the application needs."

2) VDDA (PIN_13) got a BEAD. After that BEAD, there are two caps in parallel 1uF and 100nF to GND, correct?

AN 4488: "Additional precautions can be taken to filter analog noise:

– VDDA can be connected to VDD through a ferrite bead.

– The VREF+ pin can be connected to VDDA through a resistor."

As example check the MB1136-Nucleo STM32F446 schematic:

https://www.st.com/resource/en/schematic_pack/nucleo_64pins_sch.zip

or the MB997-STM32F407 Discovery one :

https://www.st.com/resource/en/schematic_pack/mb997-f407vgt6-e01_schematic.pdf

3) i placed a picture of my Layout (i changed it slightly after reading AN4488). Could u please have a short look?

VDDA (Pin 13) capacitors are missing ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-30 01:40 PM

VCAP needs a capacitor, guessing 4.7uF in the single up case, but at least 2.2uF, this is for the onboard LDO (1.25V)

Bulk capacitors are there to supply instantaneous current, ie CMOS switching current, they play a different role to the decoupling capacitors which are there to pass high frequency noise.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-30 01:51 PM

yes, thanks. In parallel I also found (google) that they are used if the internal voltage regulator is bypassed.

whats about the rest? Are you ok with it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-05 09:18 AM

Hi @JDirk.1 ,

You need to refer to AN4488 (Getting started with STM32F4xxxx MCU hardware development).

-Amel

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-05 11:50 AM

Hi Amel,

many thanks for your reply!

I read the document, indeed really helpful. But some questions are left open to me. Most probably for someone with more experience its obvious and the AN4488 is self-explaining. But I need some help, maybe you could support?

1) I learned from AN4488 that i need a 10uF capacitor in parallel to the 100nF. On the pcb, where is the right place to put that cap? Are there any recomendations?

2) VDDA (PIN_13) got a BEAD. After that BEAD, there are two caps in parallel 1uF and 100nF to GND, correct?

3) i placed a picture of my Layout (i changed it slightly after reading AN4488). Could u please have a short look?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-21 01:56 AM

Hello,

1) On the pcb, where is the right place to put that cap? Are there any recomendations?

AN4488:

"8.3 Power supply decoupling

All power supply and ground pins must be properly connected to the power supplies. These

connections, including pads, tracks and vias should have as low impedance as possible.

This is typically achieved with thick track widths and, preferably, the use of dedicated power

supply planes in multilayer PCBs.

In addition, each power supply pair should be decoupled with filtering Ceramic capacitors

(100 nF) and one single Tantalum or Ceramic capacitor (min. 4.7 µF typ.10 µF) connected in

parallel. These capacitors need to be placed as close as possible to, or below, the

appropriate pins on the underside of the PCB. Typical values are 10 nF to 100 nF, but exact

values depend on the application needs."

2) VDDA (PIN_13) got a BEAD. After that BEAD, there are two caps in parallel 1uF and 100nF to GND, correct?

AN 4488: "Additional precautions can be taken to filter analog noise:

– VDDA can be connected to VDD through a ferrite bead.

– The VREF+ pin can be connected to VDDA through a resistor."

As example check the MB1136-Nucleo STM32F446 schematic:

https://www.st.com/resource/en/schematic_pack/nucleo_64pins_sch.zip

or the MB997-STM32F407 Discovery one :

https://www.st.com/resource/en/schematic_pack/mb997-f407vgt6-e01_schematic.pdf

3) i placed a picture of my Layout (i changed it slightly after reading AN4488). Could u please have a short look?

VDDA (Pin 13) capacitors are missing ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-04-21 11:56 AM

Thank you very much! Yes, two capacitors for PIN 13 were missing. I added them. I also learned i have to place them before the Bead, close to the PIN.

The question for the 10uF (where to place it) for the package was not answered but i found out that i need to place it close to the source of VCC.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-05-22 01:58 AM

The VCC source has it's own capacitors, but the C9 10uF is a bulk local source for the MCU close to it. VCC must be routed first to the C9 and from that further to C2-7 placed directly at VDD/VBAT pins.

- Wrong wiring for SPI? and SPI (MISO) not responding in STM32 MCUs Boards and hardware tools

- STM32F411C minimal wiring? in STM32 MCUs Boards and hardware tools

- STM32F4 A/D Input Bias Current in STM32 MCUs Products

- I am having an issue with VCAP pin and dont know how to fix it. in STM32 MCUs Boards and hardware tools