- STMicroelectronics Community

- Product forums

- ST25 NFC/RFID tags and readers

- Can't Detect Execution of Query Command ST25RU3993

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can't Detect Execution of Query Command ST25RU3993

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-02 05:34 AM

Hi,

I am developing a product based on the AS3993, AKA ST25RU3993. I have been using the FEMTO module (by AMS) to test my application code.

So far I was able to verify the initialization, SPI, interrupt line, cristall stabilization and PLL lock. Everything seems to be OK.

I am now trying to read a TAG.

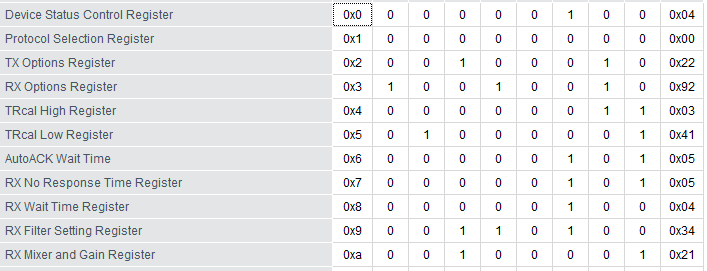

Using the defautl configurations of the FEMTO, as follow:

In order to start reading a tag. I first write the values above in the registers, then I enable the bit RF_ON on register 0x00.

After send the Query command 0x98 and write the following bytes to the FIFO:

//0b00

//dr = 0b01//m = 0b10//Trext = 0b000x18

//sel = 0b00

//session = 0b00//target = 0b00//q = 0b000x00

After that I start to wait for the end of tx interrupt, but I detect a irq_noresp instead.

Any insights?

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-28 01:54 AM

Hello Tiago,

Sorry for the late reply. We moved our community platform and had to wait until all content was transferred.

Concerning your question:

- For the session setting, please change register 0x8 from 0x04 to 0x0B to increase the rx waiting time.

- 0x0B is the default value for the Gen2 Settings you are using (LF 256, M4, Tari 25). You may increase it further to rule out a timing issue.

- Please make sure that when writing register 0x3E you also write register 0x3D (with 0x00 in your case)

- Try to send the Block_Rx command (0x96) prior to the Query command (0x98)

The preamble detect error and FIFO overflow indicates a failed reception process. The Block_Rx should compensate for that by disabling the receive decoder during the transmission of Query and the FIFO content.

If you still experience problems, I would suggest to use tr_ext (extended preamble) in the Gen2 settings:

- Rx options register 0x3, set value to 0x9A

Best regards,

Finnley

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-06-05 02:32 AM

Hello Tiago,

please check your Query command and the bytes you are writing to the FIFO.

Note that DR, TRext and Target have one bit only while Q has 4 bits.

The main issue with the bytes you write to the FIFO will be that the Miller coding and BLF will be incorrect.

Assuming you would like to use DR = 1, Target = 0 and Q = 0000 you should be writing the bytes 0x30 and 0x00 to the FIFO.

Regards,

B

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-07-04 12:05 PM

Hi Bart,

Thank you for reply. Yes, I noticed that. Even though I made this change, my code still does not work.

I am sure that my hardware is working, because I have been using the FEMTO 2.1 from AMS to test my code. My SPI communiction is also correct, I can read and write the registers in FEMTO.

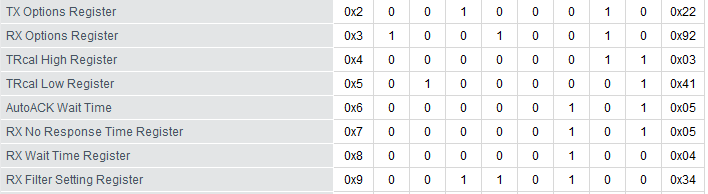

I am using the following values to set a session to try read a tag:

Register Description Address Value

After that I try to read a tag by doing the following:

1 - Set the register 0x3E with 0x1E - Sending 1 byte and 7 bits to FIFO

2 - Send the Query command - 0x98

3 - Write 0x30 0x00 in FIFO

4 - Aftet that I detect the end of transmission interrupt

5 - I wait for the end of reception interrupt

But I detect the values 0x01 in register 0x38 (Preamble detect error / FIFO overflow error) and 0x50 in register 0x37 (Bits Irq_err and Irq_rx high ). I was expecting to detect only Irq_rx high.

I have no idea what I am doing wrong.

Any idea is very much appreciated. Thank you for your time.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-08-28 01:54 AM

Hello Tiago,

Sorry for the late reply. We moved our community platform and had to wait until all content was transferred.

Concerning your question:

- For the session setting, please change register 0x8 from 0x04 to 0x0B to increase the rx waiting time.

- 0x0B is the default value for the Gen2 Settings you are using (LF 256, M4, Tari 25). You may increase it further to rule out a timing issue.

- Please make sure that when writing register 0x3E you also write register 0x3D (with 0x00 in your case)

- Try to send the Block_Rx command (0x96) prior to the Query command (0x98)

The preamble detect error and FIFO overflow indicates a failed reception process. The Block_Rx should compensate for that by disabling the receive decoder during the transmission of Query and the FIFO content.

If you still experience problems, I would suggest to use tr_ext (extended preamble) in the Gen2 settings:

- Rx options register 0x3, set value to 0x9A

Best regards,

Finnley

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-01-21 09:04 PM

Hi Tiago,

Have you resolved this problem? I come across the same problem, but have no idea as well...

- System crashing HTTP execution with GSM module in STM32 MCUs products

- About capturing with SerialWireViewer in a openOCD in STM32CubeIDE (MCUs)

- Cube MX + ecosystem 5 + custom stm32mp153 board results in missing dtb needed for optee build in STM32 MPUs Other tools

- Failed to execute MI command in STM32CubeIDE (MCUs)

- Failed to execute MI Command Error in STM32CubeIDE (MCUs)