- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs products

- Change PWM polarity at update event with STM32 Tim...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Change PWM polarity at update event with STM32 Timers?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-30 07:54 AM

I am using the adanced control and the general purpose timers witch the STM32F334K8T6 to drive one half-bridge and one full-bridge.

The problem lies with the full bridge:

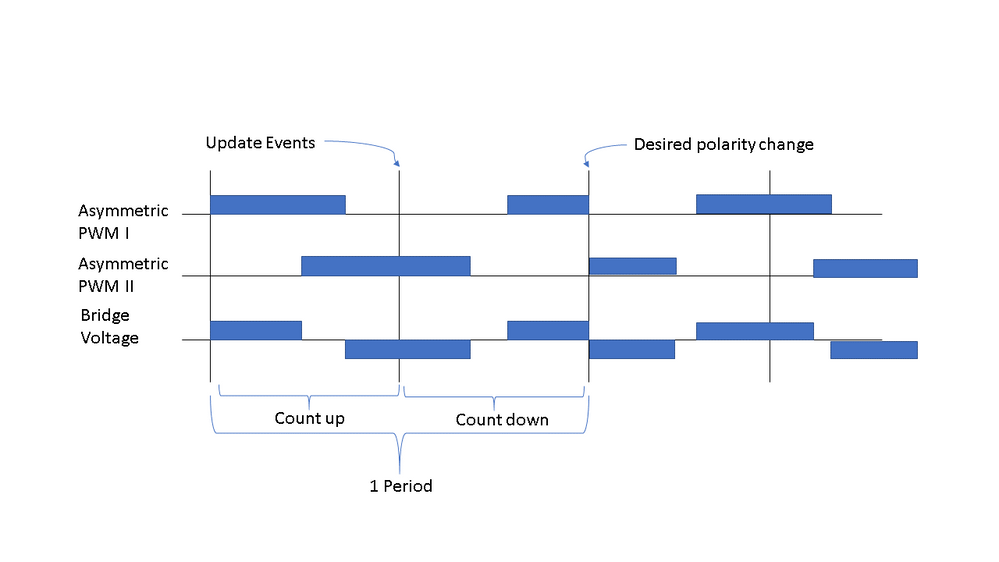

I use the general purpose timer with two times asymmetrical PWM (center aligned mode) which gives me a lot of freedom. Period and all Duty-Cycles are preloaded and always refreshed at the update event. However, I would like to change polarity of the two signals on an update event, too. I can change polarity but what is the best way changing it at the right moment (when the update event occurs).

If I am not mistaken there is no hardware solution for this. What do you propose? Should i poll the counter value or do it by some kind of intterupt? Periods are comparably short (10us), so an update event occurs every 5us.

I hope that the attached figure helps you to understand what I mean.

Thanks in advance,

Samuel

- Labels:

-

STM32F3 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-05-30 10:17 AM

Probably the easiest is to set up a DMA triggered by the update, to write the required value into TIMx_CCER.

There will be a lag of a couple of system clocks between the update and the actual polarity change, given by the DMA operation.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-03 10:24 PM

Thanks a lot, this works just fine. The lag is very small when the priority of the DMA transfer is high. This is probably the most elegant way of doing it.

Samuel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 11:50 AM

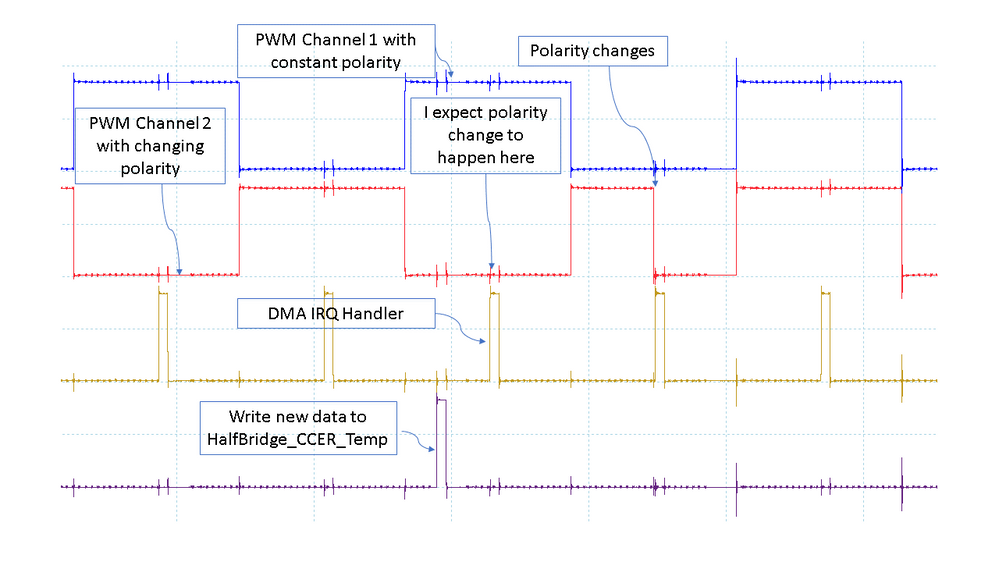

However, there is one further problem that I have noticed now. The polarity change happens later than expected.

I start the DMA in circular mode with a data length of 1.

HAL_DMA_Start_IT(&HalfBridge_DMAHandle, (uint32_t) &HalfBridge_CCER_Temp,(uint32_t) &HalfBridge_Capture_Compare_Enable_Register, 1);

I write new Data to the variable HalfBridge_CCER_Temp, but at the next DMA transfer, the old data is transferred. At the next update event the desired polarity change occurs rapidly. I have a attached a measurement to make things more clear. Do you have any idea, what could be the problem or what I am missing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 01:17 PM

Very interesting.

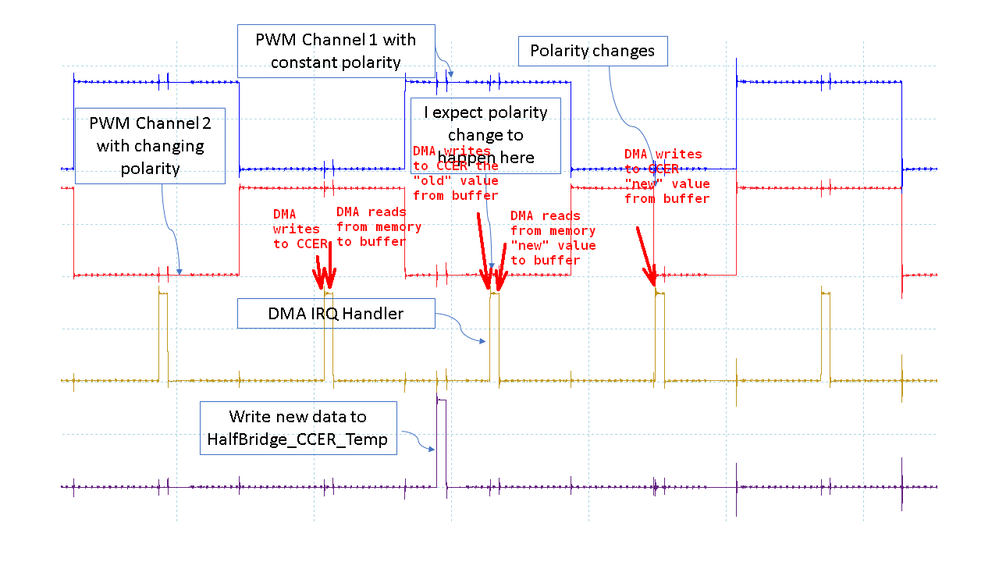

Most probably, the issue is caused by DMA buffering on the memory port.

I'm not sure what would be the best workaround, in case you can't bring writing new data more forward. You can try to swap the memory and peripheral ports (ie. write the buffer-in-memory address to DMA_CPARx and the TIMx_CCER address to DMA_CMARx; or you can stop/start the DMA when the value changes (you maybe don't need to have circular DMA anyway, so then you'd need just enable DMA).

Unfortunately, this issue is not explained in AN2548.

There's only one rather cryptic sentence at the end of 4.1.2, which says "opposite direction (peripheral to memory)" but the whole 4.1.2 (and 4.1.1) deals with peripheral-to-memory transfers. So, there's no discussion of memory-to-peripheral transfers, whatsoever.

@Imen DAHMEN , can AN2548 please be updated with detailed information on memory-to-peripheral transfers timing?

Thanks,

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-04 01:43 PM

Thanks so much!

Indeed, changing the direction from memory_to_peripheral to peripheral_to_memory seemes to solve the problem. I was sure that this parameters was set correctly. However, now the value is transferred at the next update event.

Best regards,

Samuel

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-08 05:01 AM

There was an refresh done recently on the AN2548, unfortunately before your inputs. We are already preparing more precise analysis of the timing for next release. I'm glad there is demand for this kind of information.

Thank you,

Jarda

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-08 05:04 AM

How recently?

Freshly downloaded AN2548 shows me rev.6 9-May-2019 with only nominal changes (List of supported products extended to G0 and F3:)

(F3!~ sic! in 2019! wasn't it a thread here initiating that one, btw.?)

JW

@JHOUD

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-08 05:08 AM

Revision 7, May 2020, It's about two weeks.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-08 05:41 AM

Hi Jarda, ,

Thanks.

The pipes in ST's web appears to be clogged at times, e.g. https://community.st.com/s/question/0D53W000005oxMJSAY/where-is-an5094-migrating-between-stm32f334303-lines-and-stm32g474xxg431xx

Can you please try to flush this one through?

Thanks,

Jan

@JHOUD

- Delay of interfacing timer is rather inconsistent in STM32 MCUs products

- G431 Config of input interrupt prevents timer 8 from working. in STM32 MCUs products

- USB Bulk XACT Error in STM32 MCUs products

- STM32F756VGH6 problem running 2 timers at the same time in STM32 MCUs products

- Triggering the Update Interrupt Flag of a One Pulse Timer with software in STM32 MCUs Embedded software