- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Re: STM32F446 - why PB12 conflicts with USB PHY?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F446 - why PB12 conflicts with USB PHY?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-06 03:16 PM

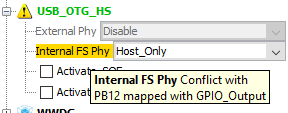

Why CubeMX 4.24 says that PB12 conflicts with USB_OTG_HS when external HS PHY is not is use?

The MCU is F446ZCT, its USB HS core is in FS, host only mode, Activate_SOF and Activate_VBUS unchecked.

PB12 can have two alternate functions for USB HS core - but both are related only to HS mode, correct?

So why conflict with the PHY in FS internal PHY mode?

(and, by the way, what does ''Activate_VBUS'' in host mode? I use a different output pin to switch VBUS to the port).

Thanks,

-- pavel

#usb-fs #cubemx-v4.24

#usb-fs #cubemx-v4.24

Solved! Go to Solution.

- Labels:

-

STM32CubeMX

-

USB

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-07 09:53 AM

Hi

pavel_a

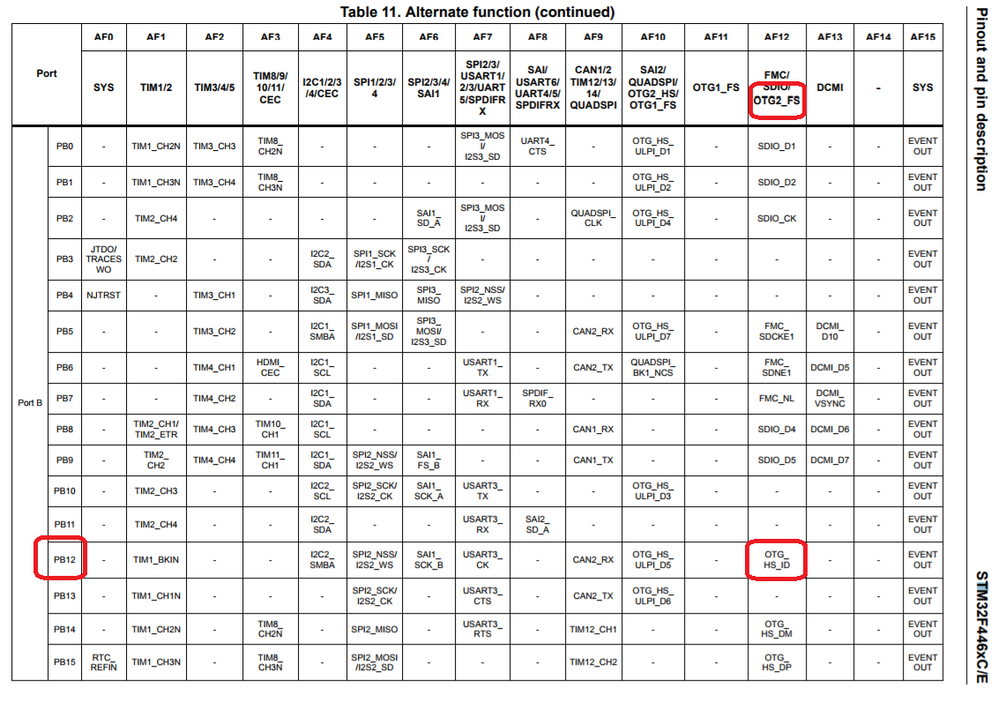

,On the datasheet, we are mentioning that the STM32F446 MCU have:

- USB 2.0 full-speed device/host/OTG controller with on-chip PHY : (OTG1_FS through GPIOA ).

- USB 2.0 high-speed/full-speed device/host/OTG controller with dedicated DMA, on-chip full-speed PHY (OTG2_FS through GPIOB) and ULPI (OTG2_HS).

If you are using the second on chip FS PHY (GPIOB), the related pins are described as HS because they are linked to the USB 2.0 high-speed/full-speed device/host/OTG controller.

On the datasheet, you may notice that the PB12 is the OTG_HS_ID in the OTG2_FS peripheral.You may also notice that also PB14 and PB15 are mentioned as ''USB_OTG_

H

S_DM'' and ''USB_OTG_H

S_DP''.Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-07 09:53 AM

Hi

pavel_a

,On the datasheet, we are mentioning that the STM32F446 MCU have:

- USB 2.0 full-speed device/host/OTG controller with on-chip PHY : (OTG1_FS through GPIOA ).

- USB 2.0 high-speed/full-speed device/host/OTG controller with dedicated DMA, on-chip full-speed PHY (OTG2_FS through GPIOB) and ULPI (OTG2_HS).

If you are using the second on chip FS PHY (GPIOB), the related pins are described as HS because they are linked to the USB 2.0 high-speed/full-speed device/host/OTG controller.

On the datasheet, you may notice that the PB12 is the OTG_HS_ID in the OTG2_FS peripheral.You may also notice that also PB14 and PB15 are mentioned as ''USB_OTG_

H

S_DM'' and ''USB_OTG_H

S_DP''.Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-07 02:12 PM

Thank you, Khouloud

-- pa

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-07 05:30 PM

Khouloud,

in the opening post, Pavel wrote:

host only mode

What would be the function of ID pin in host-only mode?

Host only

– The force host mode bit (FHMOD) in the OTG USB configuration register(OTG_GUSBCFG) forces the OTG_FS/OTG_HS core to work as a USB host-only.In this case, the ID line is ignored even if present on the USB connector.Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-08 04:24 AM

Hi Jan,

Let me check this point. I will come back to you ASAP.

Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-09 02:00 AM

Hello,

Waclawek.Jan

, Ihave checked this point and you are right.pavel_a

,the yellow warning on CubeMX indicates that at least one mode configuration is no longer available (Colored in red: OTG/Dual_Role_Device in your case). I apologize if my first answer was misleading. The good news is, if you're in 'Host only' mode, the PB12 pin could be used by other peripherals.Khouloud.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-09 09:50 AM

Thank you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-03-12 03:22 AM

You're always welcome

- eMMC 8-bit mode is not available for STM32N657X0H3Q? in STM32CubeMX (MCUs)

- Issue with Multiple ADCs and DMA Configuration on STM32G474RET6 in STM32CubeIDE (MCUs)

- Clock generation error - STM32CubeIDE 1.16 with STM32F446RE in STM32CubeIDE (MCUs)

- UART2 Status: Partly disabled conflict with PA mapped with GPIO_Output in STM32CubeMX (MCUs)

- H7 firmware v1.11.2 conflicting types in stm32h7xx_hal_hcd.c and in stm32h7xx_ll_usb.c in STM32CubeMX (MCUs)