[SOLVED] STM32F429 acknowledging timer6 interrupt

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-27 11:42 PM

I created some simple project in CubeMX for testing timer6 functionality. I configured PSC (prescaler) and ARR (automatic reload) registers. For now the interrupt handler is running correctly (it is running at calculated period), however I needed to add some special code in the end of this handler:

void TIM6_DAC_IRQHandler(void)

{

/* USER CODE BEGIN TIM6_DAC_IRQn 0 */

uint32_t z;

static uint32_t y = 1;

y ^= 1;

set_gpio(y);

htim6.Instance->SR = 0;

z = htim6.Instance->SR;

}to get it working properly.

I mean - in the 10th line I'm trying to acknowledge the interrupt flag (clear it in SR status register ). It should work but it doesn't. I have to add the 11th line to get it work.

As the proper work I mean that the blue led is blinking accordingly to the set period. Blinking led is done by set_gpio() procedure.

The strange thing is that when there is no the 11th line the program doesn't work properly.

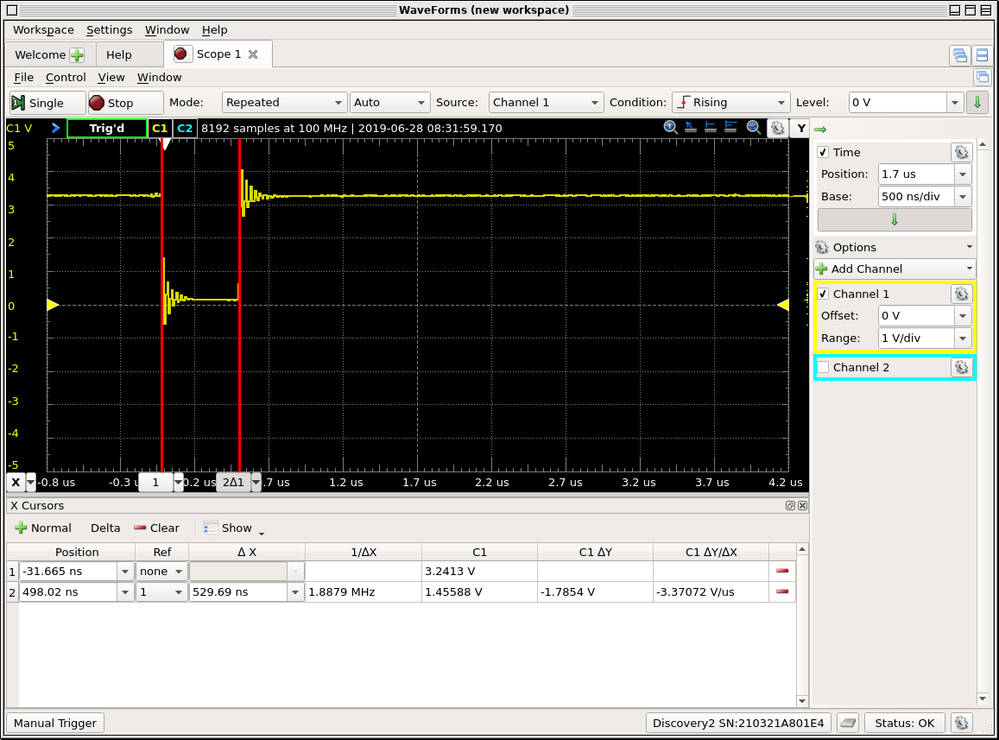

I thought that zeroing the SR should acknowledge the interrupt ans wait for the next timer invocation, but it doesn't. I've made screenshot from oscilloscope connected to the LED gpio.

As we can see there is very short transition from high level to low level for 529ns. It is too short for set period in PSC and ARR registers, because it should have about 120ms.

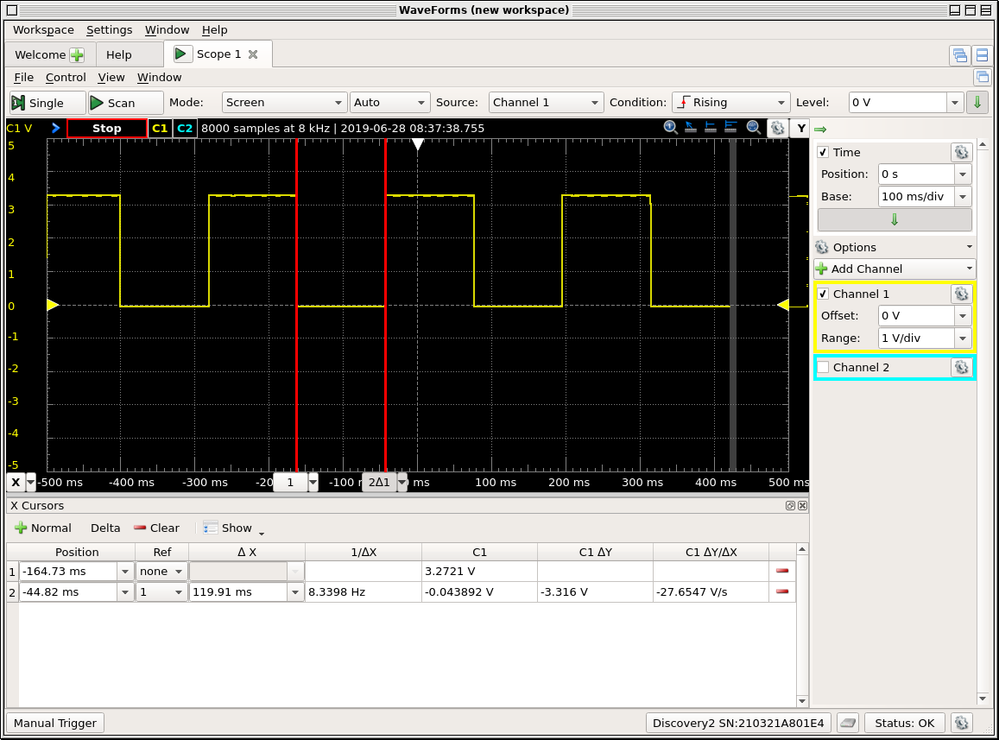

I've made also screenshot when there is 11th line added - and it looks like this:

As we can see now the period is about 119.91ms - and it is as should be.

Anyone could explain this effect? Why just adding reading from SR register (in 11th line) causes the program to work correctly? Did I miss something or doing wrong?

Solved! Go to Solution.

- Labels:

-

STM32CubeMX

-

STM32F4 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-28 12:14 AM

This is a known effect. It takes time while the zeroing of interrupt flag propagates from the timer into the NVIC (interupt controller), and if upon exiting from ISR the processor/NVIC still sees the interrupt flag being high, the processor starts executing (tail-chaining) another ISR.

Place the status register clear as the very first line in the ISR.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-28 12:14 AM

This is a known effect. It takes time while the zeroing of interrupt flag propagates from the timer into the NVIC (interupt controller), and if upon exiting from ISR the processor/NVIC still sees the interrupt flag being high, the processor starts executing (tail-chaining) another ISR.

Place the status register clear as the very first line in the ISR.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-06-28 12:35 AM

Thank you for rapid answer. Your solution helped me.