- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeMX (MCUs)

- Re: CubeMX 6.2 + HAL H7 1.9 limits the ADC clock s...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

CubeMX 6.2 + HAL H7 1.9 limits the ADC clock source to 80MHz in the Clock Configuration tab

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-03 4:42 AM

The max ADC clock is 50MHz but the source can be divided by up to 256 so there is no need to limit the source frequency

@Khouloud ZEMMELI

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-05 5:56 AM

Hi @Mikhail Z ,

Actually, the maximum ADC frequency depends from the voltage scale value, and according to RM, the Max value cannot exceed the 80Mhz.

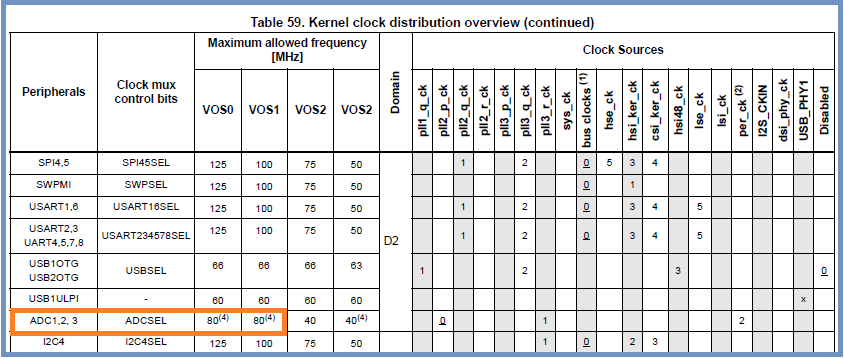

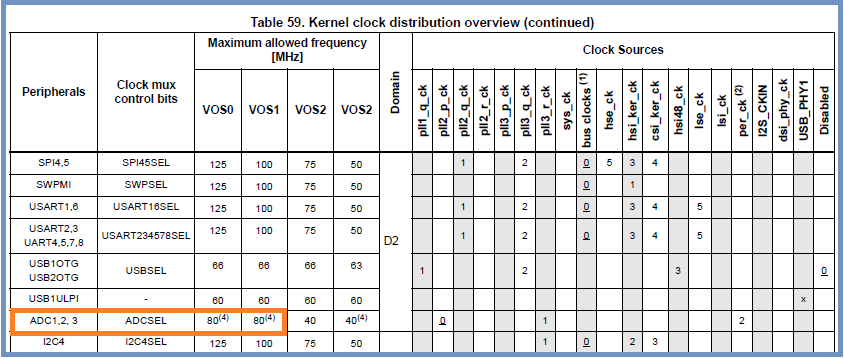

In fact, when the Power regulator voltage scale is set to 0 or 1, the Max ADC freq equal to 80MHz, in case when the Power regulator voltage scale is set to 2 or 3, its equal to 40 MHz (for more details, please refer to the Table 59 in the RM).

Hope my answer helped you, when your question is answered, please close this topic by choosing Select as Best the reply that answered you, this will help others to find that answer faster.

Thanks for your contribution, Khouloud

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-03 7:23 AM

Hello @Mikhail Z

Could you please specify the part number that you are using?

Thanks, Khouloud

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-03 9:48 AM

H743ZI

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-05 5:56 AM

Hi @Mikhail Z ,

Actually, the maximum ADC frequency depends from the voltage scale value, and according to RM, the Max value cannot exceed the 80Mhz.

In fact, when the Power regulator voltage scale is set to 0 or 1, the Max ADC freq equal to 80MHz, in case when the Power regulator voltage scale is set to 2 or 3, its equal to 40 MHz (for more details, please refer to the Table 59 in the RM).

Hope my answer helped you, when your question is answered, please close this topic by choosing Select as Best the reply that answered you, this will help others to find that answer faster.

Thanks for your contribution, Khouloud

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2021-03-11 12:56 AM

@Khouloud ZEMMELI , thank you for clarification. I just don't understand how it is possible to make the 50MHz ADC clock since for STM32H743 ver. V the minimum clock divider is 2 (so for 50MHz at least 100MHz kernel clock is needed).

- Problem: recovering ADC value in STM32CubeIDE (MCUs)

- Issues when generating a ML inference project for the Nucleo STM32N657 in STM32CubeIDE (MCUs)

- Issue with Code Generation in STM32CubeIDE for STM32H747 in STM32CubeIDE (MCUs)

- "Dwarf Error" error after new installation in STM32CubeIDE (MCUs)

- STM32H5xx - CUBE MX 6.13 - Error activating RTC Clock source for Backup register access in STM32CubeMX (MCUs)