- STMicroelectronics Community

- STM32 MCUs Software development tools

- STM32CubeIDE (MCUs)

- Re: Can't setup I2S master clock output on STM32F3...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Can't setup I2S master clock output on STM32F303CBT6 in IOC editor

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-01 08:57 PM - edited 2023-11-11 12:16 AM

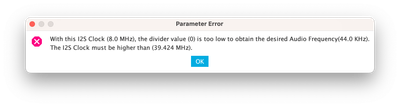

Hi, I'm trying to set up the I2S of STM32F303CBT6. Everything was fine until I checked the box "Master Clock Output", it said "With this I2S Clock (8.0 MHz), the divider value (0) is too low to obtain the desired Audio Frequency(44.0 KHz). The I2S Clock must be higher than (39.424 MHz)", although I had turned on the HSE with PLL, which is 72MHz of system clock. Am I missing something or it's a problem with STM32CubeIDE itself?

Edit: Added IOC file.

Solved! Go to Solution.

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-10 07:25 AM - edited 2023-11-11 12:08 AM

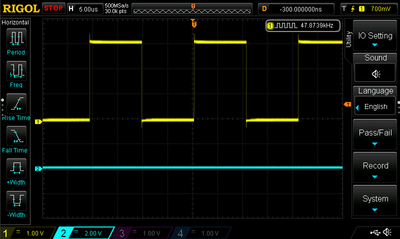

now i tried with a real F303 , to see what its doing real:

first set it to I2S , 48khz (wished) , no i2s_mco:

and 47,873KHz coming out. :) :)

(72MHz / 1504 = 47,87234 kHz --- we need @Piranha to find the mathe , how to get "50.0kHz real" here )

next: switch on mco (in debug->periph.registers MCKOE called here) -> FS now 5,9842kHz !

so DIV 1/8 switched in.

i couldnt find this behavior in manual... the secrets of STM , maybe.

ed. Jan found it ... :)

so its no basic error in Cube, the clock is divided by 8 , as soon as mco on.

simply said: unusable at > 8kHz and standard audio FS, with audio dacs, that need a master-clk.

with i2s-mco ON , max FS is 70..kHz.

next possible with direct register setting and mco:

70,314 kHzwith I2SPR at 0x202 mco then 18,00 MHz

56,252 with I2SPR at 0x302

46,8766kHz with I2SPR at 0x203

40,18kHz with I2SPR at 0x303

(real setting here: 72MHz /7 (=mco)/256 (= FS) = 40,1786 kHz)

so just this IS possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-02 12:27 AM

Welcome @yusenpai, to the community!

Please post the IOC so that people can try to understand.

Regards

/Peter

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-02 03:38 AM - edited 2023-11-02 03:39 AM

This is probably CubeMX bug, but maybe it's just incorrect wording.

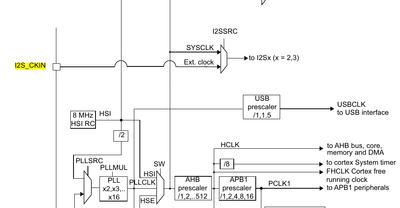

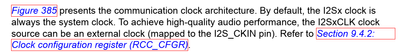

In 'F3, I2S clock is either System clock or external clock from the I2S_CKIN pin, as set by RCC_CFGR.I2SSRC; the default being the former.

So, assuming Cube "knows" this, it may try to calculate a divisor from 72MHz which would yield the requested 44.1kHz * 256 = 11.2896MHz for MCO, and fails; however, it incorrectly displays the I2S clock frequency.

The 44.1kHz audio frequency is a relatively strange one, and you have to start with chosing a primary clock (crystal) which can be successfully divided into this frequency.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

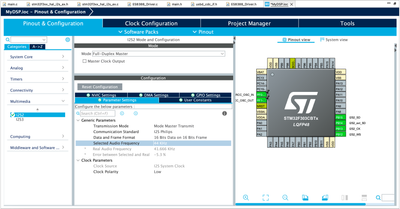

2023-11-09 09:09 PM

Hi,

For some reason, I can't upload my IOC here. In the IOC file, first I set up the HSE PLL clock with 16MHz crystal and 72MHz system clock. Then I set the I2S2 to full-duplex master mode, communication standard is I2S Philip, Data and Frame format is 16 bits data on 16 bits frame, 44KHz audio freq. When turning on Master clock output or changing to 24 bits data on 32-bit frame, I get the error message saying 8MHz is too low.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-09 09:16 PM

Hi.

I also think that's a bug. Because I set up the system clock to 72MHz first, then set up the I2S later.

Thank you for your response.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-09 11:24 PM

The file check during upload should have just been changed so that you should be able to insert IOC files. If you still have a problem with this, you can add the additional suffix .txt as a workaround.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-10 12:07 AM

i just tried same setting, 72M core, I2S on 44k , then activate mck out -> get same error:

--- but where this 8M clock coming ??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

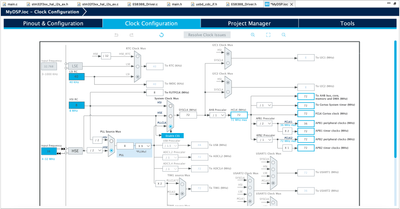

2023-11-10 12:42 AM - edited 2023-11-10 12:50 AM

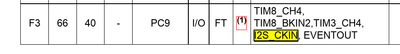

to put in i2s external clock, >48 pin case is needed...

PC9 is not here, in 48pin case. so we cannot use/switch to i2s_ckin.

but internal clock should not be 8M !

clock tree from ds :

so I2S clk should come from sysclk (72M) , not be 8M (...HSI RC is 8M ??)

who is wrong here ? Cube or datasheet ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-10 07:25 AM - edited 2023-11-11 12:08 AM

now i tried with a real F303 , to see what its doing real:

first set it to I2S , 48khz (wished) , no i2s_mco:

and 47,873KHz coming out. :) :)

(72MHz / 1504 = 47,87234 kHz --- we need @Piranha to find the mathe , how to get "50.0kHz real" here )

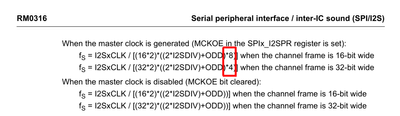

next: switch on mco (in debug->periph.registers MCKOE called here) -> FS now 5,9842kHz !

so DIV 1/8 switched in.

i couldnt find this behavior in manual... the secrets of STM , maybe.

ed. Jan found it ... :)

so its no basic error in Cube, the clock is divided by 8 , as soon as mco on.

simply said: unusable at > 8kHz and standard audio FS, with audio dacs, that need a master-clk.

with i2s-mco ON , max FS is 70..kHz.

next possible with direct register setting and mco:

70,314 kHzwith I2SPR at 0x202 mco then 18,00 MHz

56,252 with I2SPR at 0x302

46,8766kHz with I2SPR at 0x203

40,18kHz with I2SPR at 0x303

(real setting here: 72MHz /7 (=mco)/256 (= FS) = 40,1786 kHz)

so just this IS possible.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-10 11:36 PM

next: switch on mco (in debug->periph.registers MCKOE called here) -> FS now 5,9842kHz !

so DIV 1/8 switched in.

i couldnt find this behavior in manual.

As I've said above, if your goal is to have a particular audio frequency, you *start* with selecting an appropriate crystal, rather than trying to fit a integer-multiple-of-1MHz onto the desired audio frequency.

That CubeMX can't calculate is another thing. Just don't use it.

JW

- Ultra librarian creates erroneous symbols for STM32F4xxR2 in KiCAD 5 format in STM32CubeIDE (MCUs)

- Cubeide does not start (and 'Spawner Reaper') in STM32CubeIDE (MCUs)

- Bizarre: Flash content not as expected after flashing with CubeIDE, depending on compiled code in STM32CubeIDE (MCUs)

- Can't setup I2S master clock output on STM32F303CBT6 in IOC editor in STM32CubeIDE (MCUs)

- Printf Retarget only works with syscalls.c in STM32 VSCode extension (MCUs)