- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs Products

- Re: STM32MP157AAA3 use LPDDR3?

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32MP157AAA3 use LPDDR3?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-05 10:46 PM

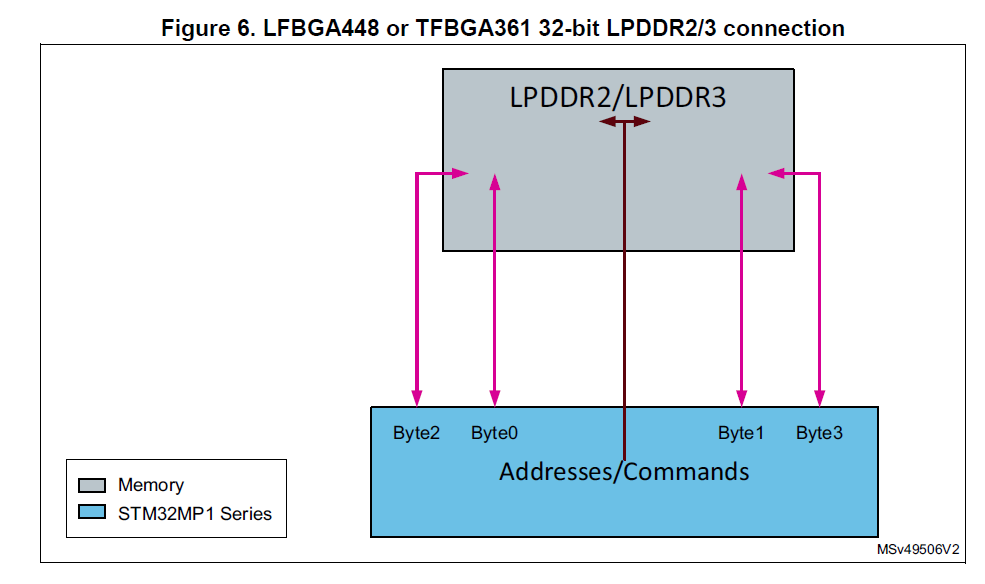

I designed a PCB using LPDDR3 and STM32MP157AAA3 MPU, but I accidentally found that u does not support, this is not a pit man? Why is this diagram on the DDR instruction manual AN5122, I'm designing it accordingto this. But now pcb has produced how to solve this problem?

@st

- Labels:

-

STM32MP15 Lines

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-05 11:22 PM

Hello,

I agree that there is a mistake in AN5122, but note that LPDDR2/LPDDR3 are not supported on LFBGA packages (STM32MP15xAA and xAB) mostly because all signal integrity simulation have not been done. This was mostly because market analysis was not showing use cases with LFBGA pitch 0.8 (mainly for industrial market and/or low cost PCB) and LPDDR (higher price, smaller PCB size, low power).

From IC point of view, nothing avoid to use LPDDR2/LPDDR3 with LFBGA package, but you should confirm signal integrity on your side as we did not provide any golden routing example nor support in CubeMx tool configuration.

Once you have a uBoot SPL basic boot running, I think the CubeMx DDR tuning tool could work if you fake it during tests by using another package supporting LPDDR.

Hope this help.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-05 11:27 PM

Hello,

Thank you very much for your answer, that is to say, in fact, the chip itself is supported right? Just do we need to debug the parameters?because my pcb is currently using lpddr3, if the redesign is very troublesome.:face_screaming_in_fear: :face_screaming_in_fear: :face_screaming_in_fear:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-06 12:30 AM

Yes, same chip is used in all packages, only less signals made available.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-06 1:26 AM

Ok..Thanks a lot.

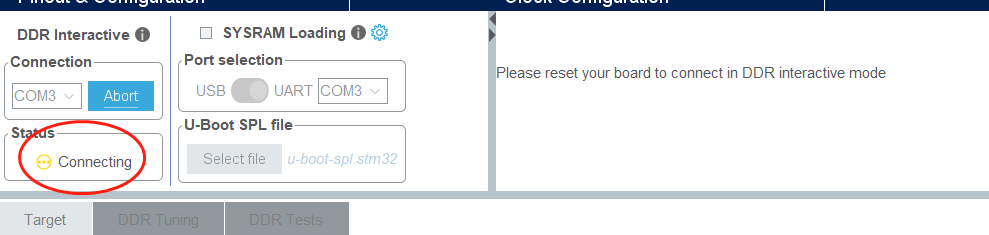

But when i used the tool for my board,i don't kown why its can't connect,the -boot-spi in sysram

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-06 1:35 AM

It's connected.:beaming_face_with_smiling_eyes: :beaming_face_with_smiling_eyes:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-06 1:37 AM

To Connect, you need to have a running uBoot SPL (basic boot) on your board (i.e. boot from a Flash or SD-Card).

If not, you should use SYSRAM loading to get it running and connect USB (FlashProgrammer is used to load it in SYSRAM instead of loaded from Flash)

You could refer to https://wiki.st.com/stm32mpu/wiki/U-Boot_SPL:_DDR_interactive_mode and CubeMX User Manual (see 'DDR Suite' section)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-06 1:46 AM

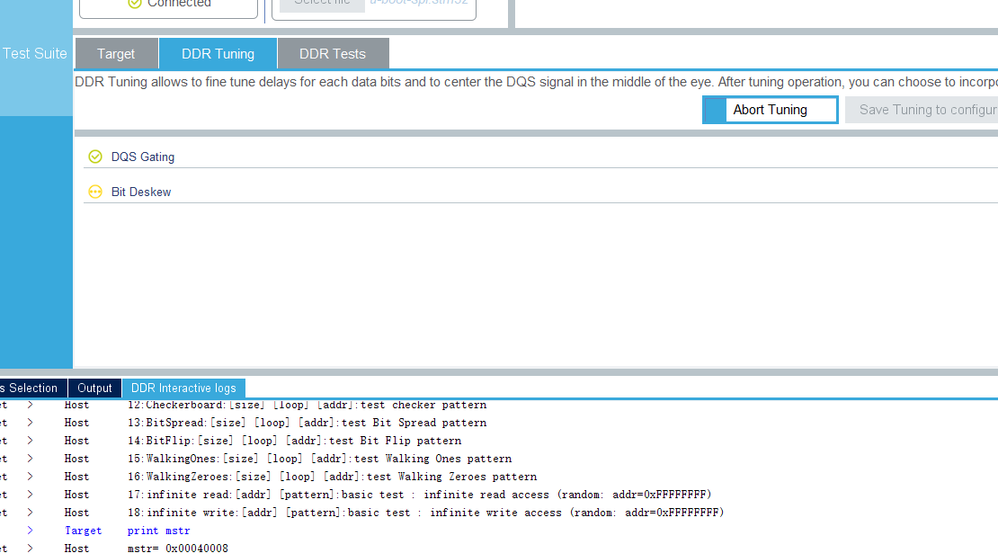

Yes,it's look great:face_with_tears_of_joy: :face_with_tears_of_joy:

but abort tuning the process is slowly?:fearful_face:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-06 2:00 AM

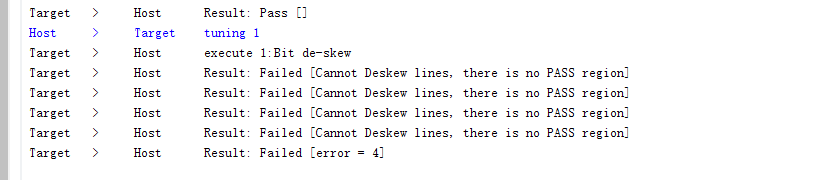

can you tell me the error was mean?:loudly_crying_face:

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-11-06 5:35 AM

Did you have something visible if you open the 'Bit Deskew'? Maybe there is too much skew between bits which mean no valid point found for all data (of a byte). But I suspect more a DDR PHY setting issue. Please look at AN5168 as well.

For information, our internal 8Gbit x32 LPDDR3 board using SK-Hynix H9CCNNNBGALAR-NXD is working with following CubeMx settings:

* DDR type / Platform LPDDR3

* freq 533MHz

* width 32

* datasheet 0

* DDR density 8

* timing mode optimized

* Scheduling/QoS options : type = 2

* address mapping : RBC

* Tc > + 85C : N

- eMMC external loader sources for stm32mp1 in STM32 MPUs Software development tools

- USB 2nd Port detection in uboot in STM32 MPUs Embedded software and solutions

- STM32MP157 and LPDDR3 unused MPU pin consideration in STM32 MPUs Products

- UBOOT RESET ISSUE in STM32 MPUs Embedded software and solutions

- USB DETECTION IN UBOOT-V2023.10 in STM32 MPUs Embedded software and solutions