- STMicroelectronics Community

- STM32 MPUs

- STM32 MPUs Products

- Re: STM32MP135 PANIC and DDR frequency error

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32MP135 PANIC and DDR frequency error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-06 8:02 AM

Hello ST community,

I am designing a board with STM32MP135 CPU and DDR3L based from STM32MP135F-DK.

DDR stress test passed successfully and tf-a files are adjusted to have I2C4 on pins used in my design (SCL on PB13 and SDA on PB7).

When I flash board there is the following message in console (debug mode enabled):

NOTICE: CPU: STM32MP135F Rev.Y

NOTICE: Model: STMicroelectronics custom STM32CubeMX board - openstlinux-5.15-y octo-kirkstone-mp1-v22.11.23

ERROR: nvmem node board_id not found

INFO: PMIC version = 0x21

INFO: Reset reason (0x35):

INFO: Power-on Reset (rst_por)

INFO: FCONF: Reading TB_FW firmware configuration file from: 0x2ffe0000

INFO: FCONF: Reading firmware configuration information for: stm32mp_io

INFO: Using USB

INFO: Instance 2

INFO: Boot used partition fsbl1

NOTICE: BL2: v2.6-stm32mp1-r2.0(debug):v2.6-dirty(a1f02f4f)

NOTICE: BL2: Built : 13:14:26, Nov 23 2021

INFO: BL2: Doing platform setup

INFO: RAM: DDR3-DDR3L 16bits 400000kHz

ERROR: DDR expected freq 400000 kHz, current is 530666 kHz

PANIC at PC : 0x2ffe588f

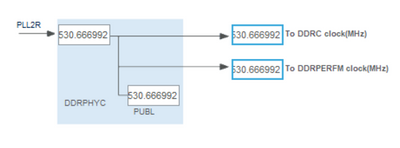

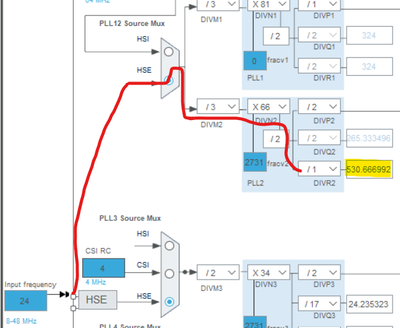

Exception mode=0x00000016 at: 0x2ffe588fConfiguration files are generated from STM32CubeMX 6.9.1 project and I noticed strange values for DIVR2 PLL that is used after by DDRPHYC. Values are with comma and I don't understand why 24MHz / 3 (DIVM2) x 66 (DIVN2) / 2 (figure 61 RM0475 Rev 1) / 1 (DIVR2) = 530.666922 instead of 264 MHz.

I tried to use generated files from STM32MP135F-DK for PLL section but unfortunately it is the same problem. I also checked HSE configuration is activated in tf-a:

clk_hse: clk-hse {

clock-frequency = <24000000>;

st,digbypass;

/* USER CODE BEGIN clk_hse */

/* USER CODE END clk_hse */

};Do you have any idea to solve this problem?

Thanks for your help.

Vincent

Solved! Go to Solution.

- Labels:

-

DDR

-

STM32MP13 Lines

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-07 5:42 AM

Hi @Vince60 ,

This panic is normal because the frequency in st,mem-speed should reflect the PLL2.DIVP output.

See

https://wiki.st.com/stm32mpu/wiki/DDRCTRL_and_DDRPHYC_device_tree_configuration#STM32CubeMX_configuration_file

https://wiki.st.com/stm32mpu/wiki/Clock_device_tree_configuration#STM32MP13x_lines

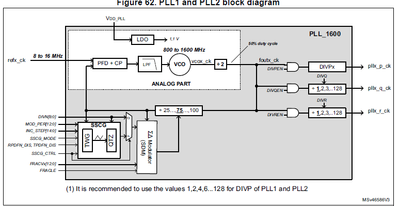

I agree that CubeMx PLL1/PLL2 drawings are slightly misleading, but the reported frequencies values are accurate.

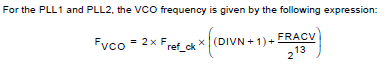

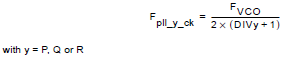

There is a /2 inside the PLL1 and PLL2, but as this /2 is within frequency loop, it is not impacting output frequency calculation (but VCO run twice faster than PLL3/PLL4 with same DIVN to get better duty cycle).

Note that if FRACV is different than 0, you should take it into account.

(note that DIVM/DIVN/DIVP in CubeMx are real division factor and does differ by 1 from DIVM/DIVN/DIVP in Device Tree/Register or RefMan formulas)

With HSE=24MHz and DIVM2=3, you get Fref_ck = 8MHz

Then with DIVN2=66 and FRACV=2731, FVCO = 1061.334 MHz

Which result on DDR clock of 530.667 MHz (with DIVR=1)

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-07 5:42 AM

Hi @Vince60 ,

This panic is normal because the frequency in st,mem-speed should reflect the PLL2.DIVP output.

See

https://wiki.st.com/stm32mpu/wiki/DDRCTRL_and_DDRPHYC_device_tree_configuration#STM32CubeMX_configuration_file

https://wiki.st.com/stm32mpu/wiki/Clock_device_tree_configuration#STM32MP13x_lines

I agree that CubeMx PLL1/PLL2 drawings are slightly misleading, but the reported frequencies values are accurate.

There is a /2 inside the PLL1 and PLL2, but as this /2 is within frequency loop, it is not impacting output frequency calculation (but VCO run twice faster than PLL3/PLL4 with same DIVN to get better duty cycle).

Note that if FRACV is different than 0, you should take it into account.

(note that DIVM/DIVN/DIVP in CubeMx are real division factor and does differ by 1 from DIVM/DIVN/DIVP in Device Tree/Register or RefMan formulas)

With HSE=24MHz and DIVM2=3, you get Fref_ck = 8MHz

Then with DIVN2=66 and FRACV=2731, FVCO = 1061.334 MHz

Which result on DDR clock of 530.667 MHz (with DIVR=1)

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 5:34 AM

Hi @PatrickF ,

Thank you for this quick answer, I updated stm32mp13-mx.dtsi file in tf-a folder with new value

#define DDR_MEM_SPEED 530666and it works fine now.

Just one more question about STM32CubeMX utility. Why fracv2 value is 2731 in my project and 5120 in DK project? I selected same HSE clock frequency (24Mhz) and same DIVM2 and DIVN2 so I expected to have same fracv2 value.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 6:31 AM

Hi,

In CubeMx, you could edit the FracV field to the value you want in order to obtain the requested value on clock outputs. 5120 Fravc is to get exactly 533000kHz

Sometimes, CubeMX do some 'fancy' automated value computation.

Beware that some DDR settings are dependent of clock frequency (e.g. refresh, timings), so even if it might barely work, do not use 400MHz settings for 533MHz DDR clock.

But 533 MHz for 530 MHz is acceptable.

Regards.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 5:25 AM

Hi @PatrickF ,

Thanks for the explanation, CubeMX project is now configured and TF-A is loaded by using STM32CubeProgrammer.

Regards

- weston-touch-calibrator on scarthgap has stopped working in STM32 MPUs Products

- [ERROR] Couldn't find any video driver in STM32 MPUs Embedded software and solutions

- Can't connect to STM32 in STM32 MPUs Boards and hardware tools

- STM32MP157 "E/TC:0 do_pm_callback:75 Suspend vref_ddr (0xde003d9d) failed: 0xffff0000" in STM32 MPUs Embedded software and solutions

- STM32MP135 NO BACKLIGHT in STM32 MPUs Embedded software and solutions