- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Wireless

- Radio frequency communication between Nucleo-WL55...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Radio frequency communication between Nucleo-WL55jc2 and radio frequency Device

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-20 6:58 AM

Hi ST experts.

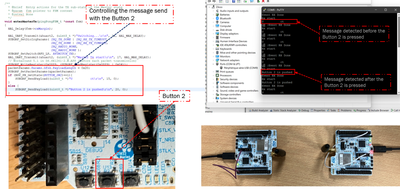

I used the pingpong sample code with the tutorial I have found in the TechForum: Link of the tutorial in order to establish the radio frequency communication between two Nucleo-WL55JC2 boards and it works.

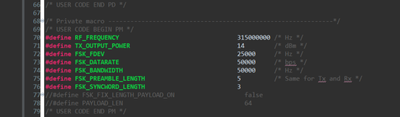

And then I tried to communicate with the device that has this configuration

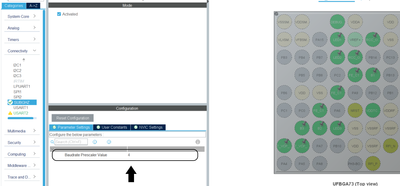

It didn't work with my code, I searched for the problem and I found on the configuration of the subghz:

What is the role of the baudrate prescaler value for the subghz configuration?

and what changes should I make?

Solved! Go to Solution.

- Labels:

-

STM32CubeMX

-

STM32WL series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-21 10:31 AM

Hello @Zayoud and welcome to the ST Community :smiling_face_with_smiling_eyes:.

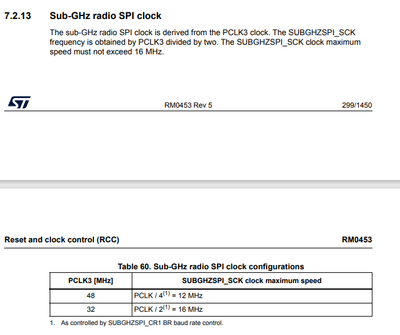

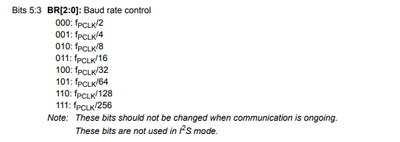

According to the RM0453, The sub-GHz radio SPI clock is derived from the PCLK3 clock. The SUBGHZSPI_SCK

frequency is obtained by PCLK3 divided by two. The SUBGHZSPI_SCK clock maximum

speed must not exceed 16 MHz. So, the baudrate prescaler value should be 4 or more in case PCLK3 clock is 48MHz or 2 in case PCLK3 clock is 32MHz.

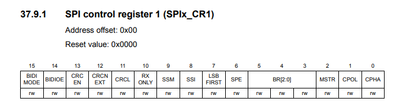

So, the baudrate prescaler value is the frequency divider value. it set exactly the 3 bits of the Baud rate control on the SUBGHZSPI_CR1:

Best regards.

Liltek Zina.

STTwo-32

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-20 7:15 AM - edited 2024-02-20 7:17 AM

@Zayoud wrote:I used the pingpong sample code with the tutorial I have found in the TechForum: Link of the tutorial

That's DigiKey's forum - nothing to do with ST.

https://forum.digikey.com/t/using-the-low-level-sub-ghz-radio-driver-for-the-stm32wl-series/18253/11

As it says there, they're throwing away ST's standard code, and doing something "different" instead - so you'd probably be better asking the actual author there what it is that he's done, and how to understand & use his code!

@Zayoud wrote:What is the role of the baudrate prescaler value for the subghz configuration?

A complex system designed from scratch never works and cannot be patched up to make it work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-02-21 10:31 AM

Hello @Zayoud and welcome to the ST Community :smiling_face_with_smiling_eyes:.

According to the RM0453, The sub-GHz radio SPI clock is derived from the PCLK3 clock. The SUBGHZSPI_SCK

frequency is obtained by PCLK3 divided by two. The SUBGHZSPI_SCK clock maximum

speed must not exceed 16 MHz. So, the baudrate prescaler value should be 4 or more in case PCLK3 clock is 48MHz or 2 in case PCLK3 clock is 32MHz.

So, the baudrate prescaler value is the frequency divider value. it set exactly the 3 bits of the Baud rate control on the SUBGHZSPI_CR1:

Best regards.

Liltek Zina.

STTwo-32

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-03 3:12 AM

Hello @STTwo-32,

I would like to express my gratitude for your previous assistance in clarifying the role of the variable. It was immensely helpful:D.

As I am currently expanding my knowledge in the domain of Radio Frequency communication, I have some inquiries regarding ST's RF products. I possess two NUCLEO-WL55JC2 boards and one NUCLEO-WL55JC1 board. Could you please confirm if either of these boards is capable of reading RF signals from any arbitrary RF device, or are they solely designed for detecting signals with a predetermined frequency?

Furthermore, I am experimenting with several RF products that utilize FSK modulation. Given the multitude of variables involved in the communication process, I would appreciate it if you could specify the critical variables that I need to identify in order to program the NUCLEO-WL55JC boards for effective communication.

In conclusion, I kindly request a link to an RF training course or a recommendation for a book that could further enhance my understanding of RF communication principles.

Thank you very much for your time and assistance.

Liltek Azyen:beaming_face_with_smiling_eyes:.

Zayoud

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-03 4:54 AM

3aslama

Thank you so much for your complement. Can you please create a new post for this question so we give it more visibility and other clients can see it. Also, could you please add more descriptions for your questions (specially the first, an example may help too).

Best Regards.

STTwo-32

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-05-07 6:00 AM

@STTwo-32 wrote:please create a new post for this question

It's here:

A complex system designed from scratch never works and cannot be patched up to make it work.

- Request for Guidance on LoRa-E5 (STM32WLE5JC) LoRa TX/RX Setup in STM32CubeIDE 2.1.0 in STM32 MCUs Wireless

- Locked H503 - unable to degug in STM32 MCUs Security

- STM32F030C: SPI Slave at 13.5 MHz with GPIO_Speed = Low for EMI reduction? in STM32 MCUs Products

- CAN communication between 3 Nucleo boards in STM32 MCUs Products

- Issue with 32 MHz Crystal Stability Affecting LoRa Gateway Communication in STM32 MCUs Wireless