- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Why FMC bus turnaround time is so long in mode...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Why FMC bus turnaround time is so long in mode D on STM32F303?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-26 08:33 AM

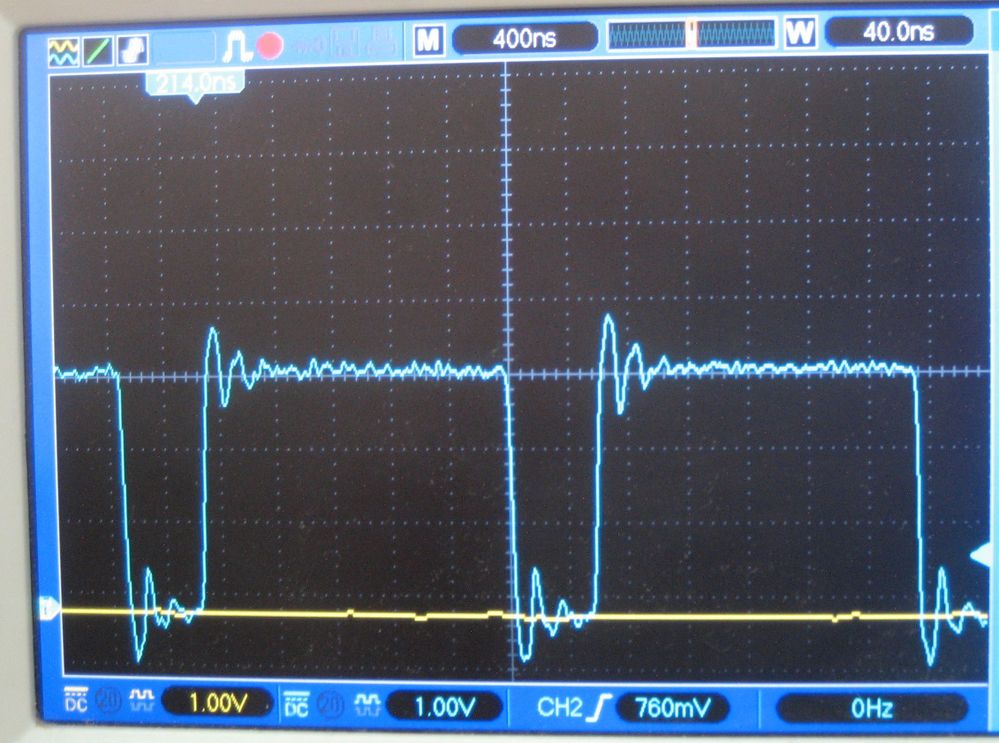

I'm using STM32F303ZE MCU's FMC(FSMC) to communicate with a special chip. FMC is cofigured in NOR/PSRAM mode, asynchronous, non multiplexed, timing mode D (see attached FMC configuration in CubeMX). FMC clock is equal to AHB MCU clock that is 70MHz. I see very long bus turnaround time between two consecutive writes into the same bank: 200ns instead of 14ns (1 HCLK clock). Bus turnaround time is set 1HCLK that is 14ns. Why real turnaround time is so big?

This oscillogram shows NE signal transitions during FMC write transactions. These write transactions are initiated by DMA controller in memory-to-memory mode. All other DMA channels are idle. Only SysTick interrupt (1ms periods) is enabled. CPU is not running (Sleep mode).

Code cofiguring and running the DMA transfer is following:

DMA1_Channel2->CCR =0;

DMA1_Channel2->CPAR = (uint32_t)(&adcZero[0]);

DMA1_Channel2->CMAR = (uint32_t)(&DDS_DATA_FMC);

DMA1_Channel2->CNDTR=100;

DMA1_Channel2->CCR = (1<<14)|(1<<0)|(1<<8)|1; // Start transfer

__wfi();Is it possible to make turnaround time shorter?

PS. If I configure FMC in mode 1, turnaround time becomes much shorter, showing that this shorter timing is achievable. Unfortunately I can't use Mode1 because external chip requires NE toggle between consecutive writes.

- Labels:

-

FMC-FSMC

-

STM32F3 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-26 12:44 PM

Maybe here not the FMC is limiting, but DMA.

Try back-to-back writes from processor.

Also, try 32-bit writes, FSMC ought to split them to 2 16-bit writes internally, and those should then reveal the real internal back-to-back delay, independent on the rest of the system.

> DMA1_Channel2->CCR = (1<<14)|(1<<0)|(1<<8)|1; // Start transfer

Did you mean

DMA1_Channel2->CCR = (1<<14)|(10<<0)|(1<<8)|1; // Start transfer

?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-27 02:27 AM

Thanks JW, this:

> DMA1_Channel2->CCR = (1<<14)|(1<<0)|(1<<8)|1; // Start transfer

shoul be:

DMA1_Channel2->CCR = (1<<14)|(1<<10)|(1<<8)|1; // Start transfer

But the timing stayed the same.

I have also tried to send 32bit data to my 16bit FMC device:

DMA1_Channel2->CCR = (1<<14)|(1<<10)|(2<<8)|1;

but this didn't change timing either.

So looks like FMC is limiting turnaround time, but I don't understand why. Page 270 of reference manual says: "The programmed bus turnaround delay is

inserted between an asynchronous read (muxed or mode D) or write transaction and any other asynchronous /synchronous read or write to or from a static bank." (Description of field BUSTURN, reg. FMC_BTR). As I wrote, programmed turnaround time is 1HCLK, but the real turnaround time is much bigger.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-29 02:20 PM

Read out and check/post content of the FMC registers.

Also, try back-to-back writes from processor, to exclude issues with DMA.

I presume you do all this experimenting on a minimal code, so that there's no potential interference from other parts of code.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-03-30 06:23 AM

Yes, the code is minimal. Moreover, the CPU is stopped with __wfi() instruction before DMA transfer.

I'll be back with FMC registers and other tests when virus quarantine will end.

- STM32H753VITx with ULPI USB3320 - corrupted data? in STM32 MCUs Products

- Syncronous Timers in STM32 MCUs Products

- Software triggered multichannel scan - callback not triggered in STM32 MCUs Embedded software

- STM32F303 Timer - Count Mismatch in STM32 MCUs Products

- STM32F303 DMA fails to collect data when ADC is running at maximum speed in STM32 MCUs Products