USB on-the-go high-speed (OTG_HS) - core setup confusion

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 5:30 AM - edited 2023-09-19 7:55 AM

In RM0456 section 73.4.3 OTG_HS core (p.3279) I found the following statement:

"The OTG_HS receives the 60 MHz clock from the reset and clock controller (RCC). This is typically generated in the PLL associated with the HS PHY and enabled in the RCC. This clock is used for driving the 60 MHz domain at high-speed (480 Mbit/s) and must be enabled prior to configuring the OTG core."

I try to configure STM32U5A9 MCU with CubeMX, but I find no option to configure USB 60MHz clock.

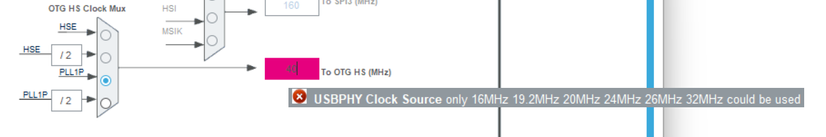

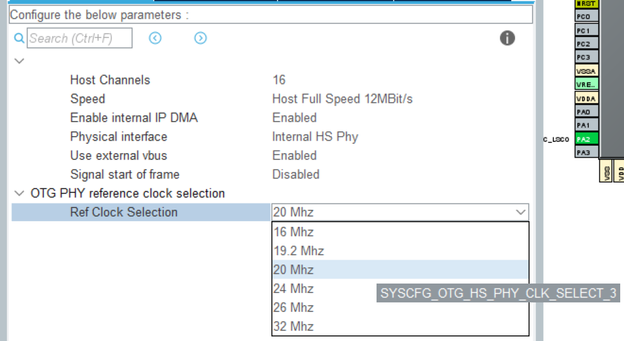

The only available clock setting called "OTG HS Clock" cannot be set to a value larger 32HMz and probably needs to match setting under "Pinout & Configuration" where this time it is called "Ref Clock selection" - see screenshots below.

Where do I set 60MHz clock as described in RM0456? Instead, CubeMX offers 16/19.2/20/24/26/32MHz clock selection. In RM0456 I found no 16/19.2/20/24/26/32MHz clock values mentioned.

Please advise. I am a bit confused.

Solved! Go to Solution.

- Labels:

-

STM32CubeMX

-

STM32U5 series

-

USB

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 6:19 AM

The OTG HS PHY PLL has only a limited set of input frequencies allowed:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 6:19 AM

The OTG HS PHY PLL has only a limited set of input frequencies allowed:

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 7:48 AM - edited 2023-09-19 7:51 AM

@waclawek.jan Thanks for pointing out this section 15.2.3. I guess, CubeMX does not fully support this USB IP yet when it comes to 60MHz clock setup, but I should be able to set it up without CubeMX. At least, there is hope:)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-19 8:17 AM - edited 2023-09-20 8:23 AM

@waclawek.jan An update. I realized that:

1. Probably missing config can be accomplished with the below HAL LL function not used in CubeMX generated code.

- HAL_SYSCFG_SetOTGPHYDisconnectThreshold(SYSCFG_OTG_HS_PHY_DISCONNECT_5_9PERCENT);

- HAL_SYSCFG_SetOTGPHYSquelchThreshold(SYSCFG_OTG_HS_PHY_SQUELCH_15PERCENT);

- HAL_SYSCFG_SetOTGPHYPreemphasisCurrent(SYSCFG_OTG_HS_PHY_PREEMP_DISABLED);

2. Probably no additional 60MHz clock config is required. The only required clock config is done in __HAL_RCC_USBPHY_CONFIG macro or directly using RCC_CCIPR2.OTGHSSEL register field (RM0456, section 11.8.47). In HAL RCC_CCIPR2_USBPHYCSEL named is used, probably so nobody can quickly figure out this is the same register and field. RM0456 section 73.4.3 is quite misleading with that respect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-20 12:56 AM - edited 2023-09-20 2:08 AM

Just a side note for anyone who might come across this topic. OTG_HS host may not be currently fully implemented in HAL. See stm32u5a9xx.h USB_OTG mess · Issue #31 · STMicroelectronics/STM32CubeU5 (github.com)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-28 10:39 PM - edited 2023-09-30 12:02 AM

@waclawek.jan OTG_HS host HAL may also have some bugs.

See: Why OTG_HS USB/USBX Host on STM32U5Axx just does not work? (2)