- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: [STM32L431] BORRSTF always SET after powering ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

[STM32L431] BORRSTF always SET after powering up

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-02 07:31 AM - edited 2023-08-02 07:46 AM

Hello,

I want to read the BORRSTF value to detect the previous reset situation during the start process. but BORRSTF always reports '1'.

BORRSTF can be clear with RMVF, but there is a problem that makes it impossible to tell whether it is an initial start or a after brown out reset.

I tried the following:

- Check ramp-up time problem of power supply. - but I didn't find anything strange.

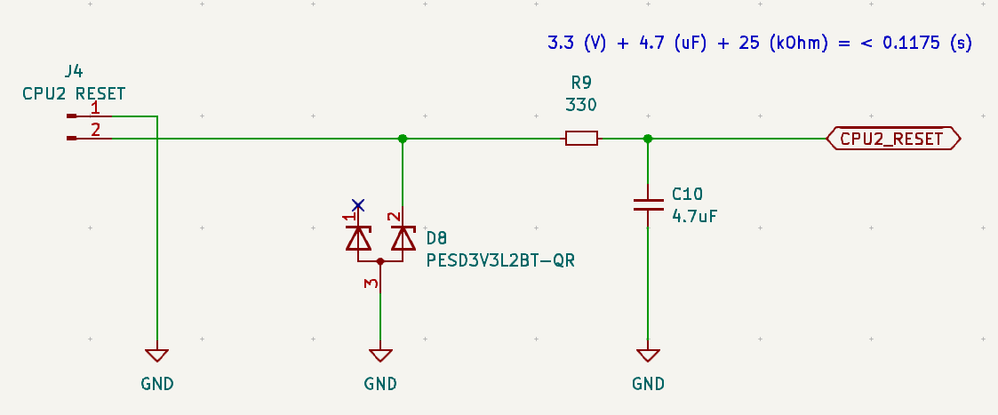

- Increase capacitance of the reset pin for the longer reset delay. - I've increased it from 0.1 uf to 4.7 uF, but problem is not solved.

I looked for similar cases, but I couldn't find the same one... Is there a problem with my design?

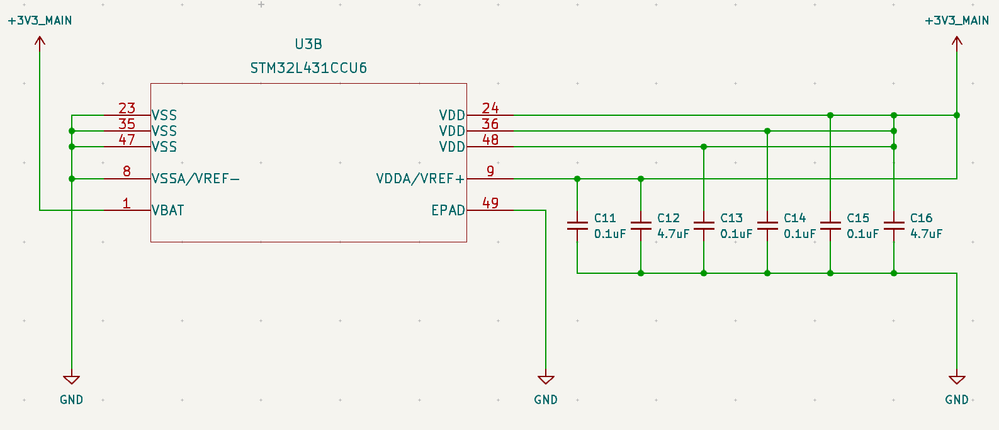

Attached power and reset circuit diagram I designed. thanks.

p.s I've found the same thing on STM32F407VGT-based PCB before year. I didn't take it seriously then, but now I want to know why.

Solved! Go to Solution.

- Labels:

-

STM32L4 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-02 01:13 PM

> why is BORRSTF active on initial power up?

0V is below the BOR threshold.

> this behavior is not documented anywhere, like RM0394 'Reference manual for STM32L4'.

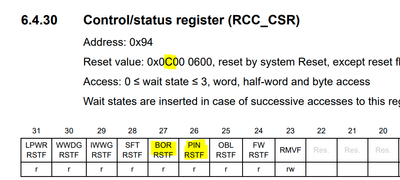

It absolutely is in there. Reset value shown that BORRSTF is high on startup.

More to your point, looks like there isn't a reliable way on here to differentiate between POR and BOR. You could set a magic value in SRAM on startup and if during the next startup it's the magic value (instead of 0x00 or 0xFF or random data), likely it was a BOR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-02 08:52 AM - edited 2023-08-02 08:55 AM

Look at all the flags to understand what happened, not just the BORRSTF. At power-on, PORRSTF is also set.

If PORRSTF and BORRSTF -> power on

If not PORRSTF and BORRSTF -> BOR

Somewhere there is a table which shows the flags for various reset conditions. If I find it, I will add it here.

Edit: the above is true for the STM32F4 family, which you mentioned. It doesn't look like there is a PORRSTF flag on the L4 family.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-02 11:09 AM - edited 2023-08-02 11:16 AM

@TDKThank you for reply. (I clicked the accepted button mistake, sorry.)

Yes, as you mentioned at the edit, STM32L4 does not have PORRSTF. according to my short experiment, BORRSTF and PINRSTF are activated at initial powering up. but it still seems unclear to me.

Just a moment ago, I found the same BORRSTF issue on evaluation board known as 'Blackpill' (STM32F411). what I'm really curious about is, why is BORRSTF active on initial power up? this behavior is not documented anywhere, like RM0394 'Reference manual for STM32L4'.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-02 01:13 PM

> why is BORRSTF active on initial power up?

0V is below the BOR threshold.

> this behavior is not documented anywhere, like RM0394 'Reference manual for STM32L4'.

It absolutely is in there. Reset value shown that BORRSTF is high on startup.

More to your point, looks like there isn't a reliable way on here to differentiate between POR and BOR. You could set a magic value in SRAM on startup and if during the next startup it's the magic value (instead of 0x00 or 0xFF or random data), likely it was a BOR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-02 08:31 PM - edited 2023-08-02 08:36 PM

@TDKThank you for your answer.

Oops, I was making a false assumption that the initial value of the CSR register would of course be filled 0. thank you for your correction. :)

I agree with you regarding POR flags. fortunately, I think it can be solve through linker settings.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-04 06:43 AM - edited 2023-08-04 06:43 AM

looks like there isn't a reliable way on here to differentiate between POR and BOR.

Is there any real difference between those? The only one I see is just a different voltage threshold levels.

- STM32L431 power consumption. in STM32 MCUs Products

- [STM32L431] BORRSTF always SET after powering up in STM32 MCUs Products

- STM32L431 strange current draw in STM32 MCUs Products

- STM32L431 can not be debugged; SWD communication failure? in STM32 MCUs Boards and hardware tools

- simple 3 Button Touch Key application using TSC on STM32L431 goes wrong when power supply drops from 3.3V to approx 3.0V then recovers to 3.3V. in STM32 MCUs Products