- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32H750B-DK ADC Sample

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32H750B-DK ADC Sample

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 2:39 AM

Hello there, I am making an osciloscope

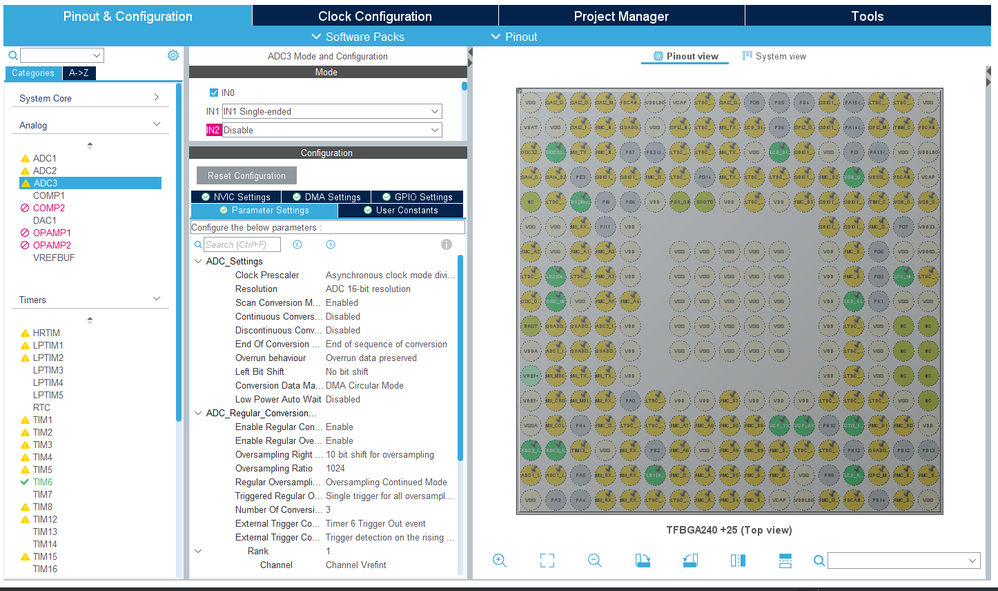

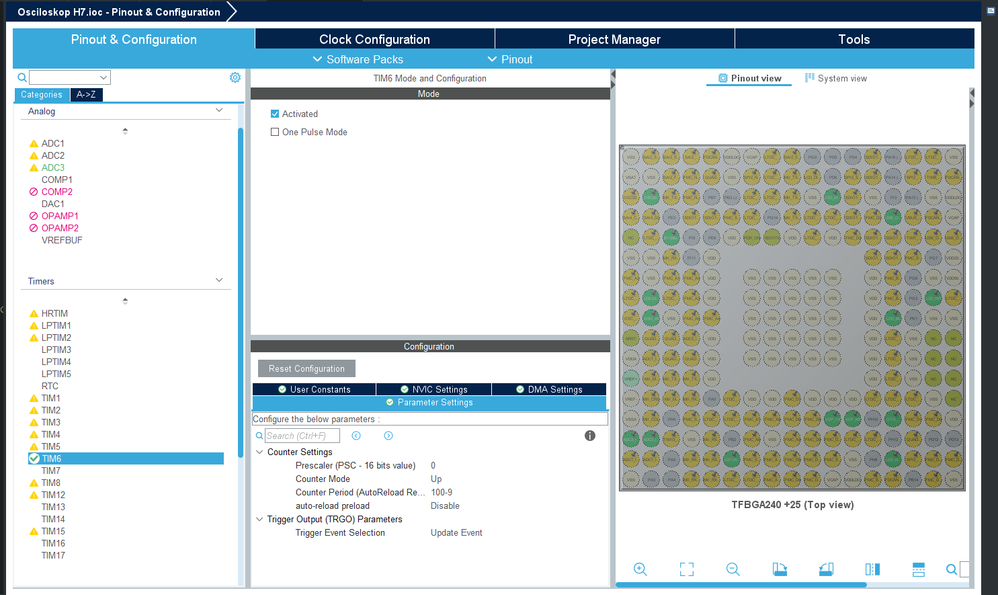

I am using ADC with configuration like this

and I am triggering my ADC with 1ms TIM6 and sending this to PC where I display it

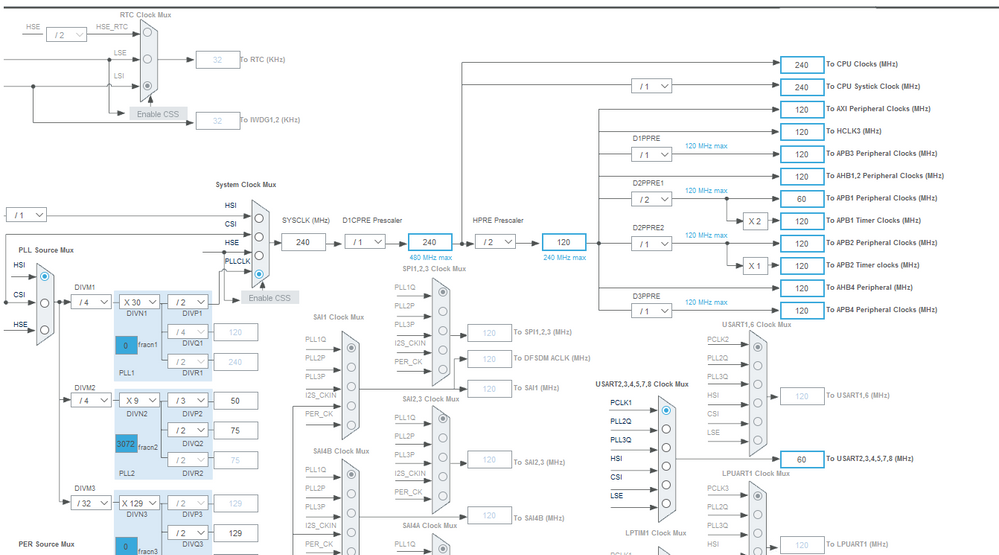

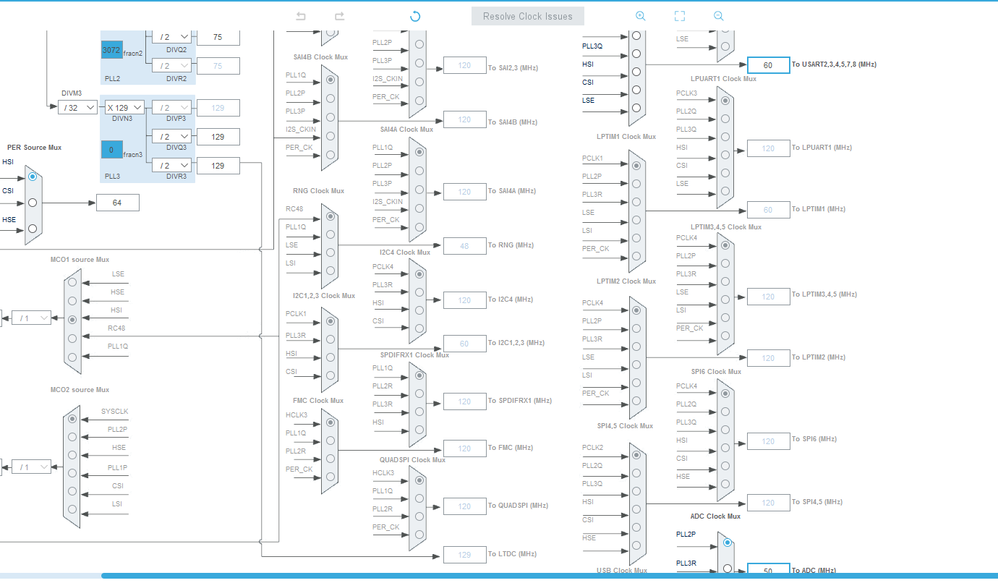

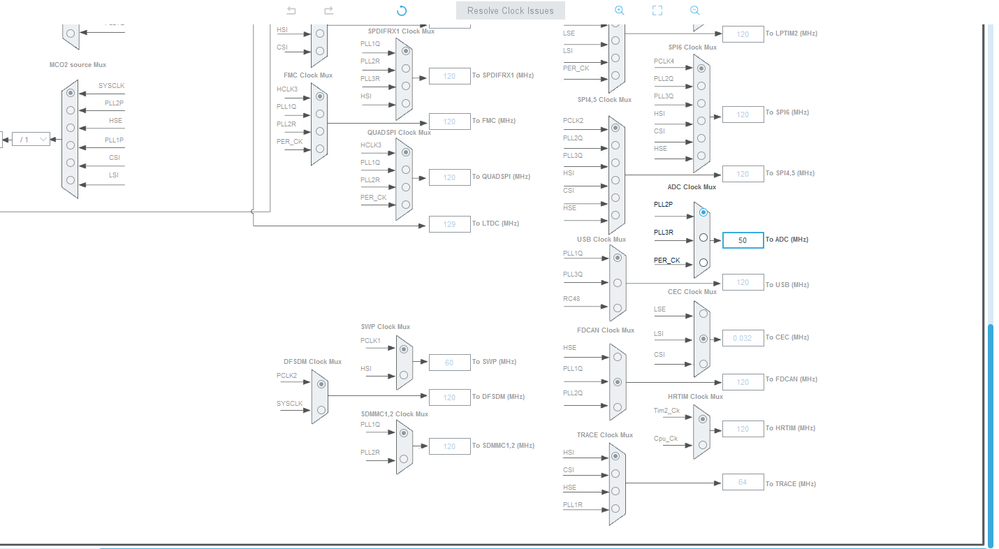

I am using 240Mhz CPU Clock and my clock configuration looks like this

Now everything works fine but the highest signal I can see is 955 Hz (which means my sample rate is probably 1.91 khz (955*2=1910 Hz)

Now I cannot figure out where this limitation comes from, I am using 240Mhz CPU clock and I am constantly triggering ADC with 1ms (I just want to know why is there this limitation, maybe if I use High speed timer, I could increase this, but thats not important right now)

I did figure out that if I increase CPU frequency (it was 72Mhz before and the highest signal I could see was even lower) that my sample rate also increases so sample rate is somehow related to CPU frequency

So why is my sample rate that low (I would expect it at least like 1Mhz or something (if I use 240Mhz CPU clock)

Thanks for Anwsering and Best Regards

- Labels:

-

ADC

-

STM32H7 series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 3:46 AM

> and I am triggering my ADC with 1ms TIM6 and sending this to PC where I display it

- Do you trigger a single conversion every 1 ms, or a burst of AD conversions? If burst, how many?

- How do you get data to the PC? If it's the UART, think about baud rate vs sample rate in bits per second.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 4:02 AM - edited 2023-09-08 4:03 AM

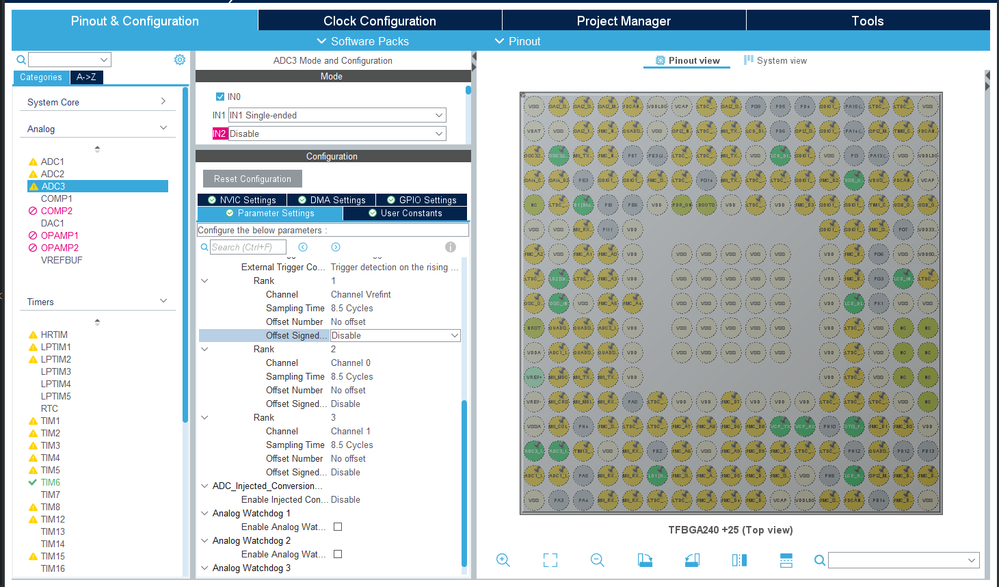

Hi there, I am triggering single conversion every 1ms (picture should show that so I believe single conversion every 1ms) (I have 3 channels if it helps any)

I am using UART to get data to PC (115200bps8n1) so I know this is my bottleneck (I assume my bottleneck is about 11.25khz sample rate (if we assume 1 bit is 1 cycle), but would still need to figure out sample rate before UART

Because I believe that raw ADC sample rate (if I would skip uart and display my data direcly on the STM32 screen for instance) is not influenced by uart

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 1:06 PM - edited 2023-09-08 1:08 PM

https://www.st.com/resource/en/datasheet/stm32h750ib.pdf

Please find the datasheet of the MCU as per attachement.

If you really need performance: Use DMA with double buffers, trigger ADC with a timer and things will go much faster. You can also use USB or ETHERNET to send data to your PC in bursts, this will also increase performance. If you want to know where your bottleneck is, do the math and use the datasheets...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 1:42 PM

I am triggering ADC with TIM6 already (TIM6 counts with 1ms (at least I think it is (was always confused on how to calculate its tick, so I just set PSC to 0 to make it easier for myself)) like pictures shows

At first would just like to find the sample rate, then when I have that I will figure out how to improve it (will probably use USB at later date or just bypass the computer and show my values direcly on STM32H750B-DK screen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-08 10:49 PM

I do not understand your statement "At first would just like to find the sample rate"; when you trigger ADC with 1 ms, then the sample rate is 1KHz?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-09 3:40 AM

Oh, ok, so if I trigger my timer with 1ms, my sample rate will always be 1kHz, regardless of ADC clock, its sampling time per channel (8.5 Cycles), its prescaler?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-09 3:59 AM

There are different ways to trigger your ADC, I presume that you trigger your ADC with the output of your timer, so then to initate a ADC conversion each time the tigger comes around. One of the things you can try to test is to reduce the duty cycle of your timer and see what the result is.

- Using VREFINT on STM32C071K8U6 for battery measurement with variable VDDA in STM32 MCUs Products

- Real audio frequency and error between selected in SAI for the STM32N6 showing 0 in STM32CubeMX (MCUs)

- STM32 + Freertos + Audio recording + FATFS. Audio really choppy and white noisy in STM32 MCUs Embedded software

- CubeL4 ADC HAL_ADC_MspInit and HAL_ADC_MspDeInit issue in STM32CubeMX (MCUs)

- N6 App OTA via UART, DFU or otherwise - not working for app image in STM32 MCUs Products