- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Stm32g0 vref beginner question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Stm32g0 vref beginner question

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-12 08:47 PM

I want to use a bidirectional current sense such as ina181 and read the values into stm32g0 Mcu.

This does not need to be super accurate (max current is +/- 500mA and just want an idea of if approaching that) but I am struggling to find a canonical circuit that makes best use of the available features of the vrefbuf and is not adding a lot of expense and complexity with external reference when just a ballpark number is needed.

it seems like using the Mcu vref+ to bias the zero on the current sense would be the best and cheapest option.

is this as simple as resistor dividing the 2.5v vref pin down to 1.65 (for 3.3v supply and symmetrical +- current) and connecting it to vref on the current sense amplifier?

also I notice a lot of designs connect vref to vdd so I assume this should not be done if using internal ref. But if I decide not to use the internal vref in the future will it be a problem that it has the divider resistance to ground connected ?

Thanks

tom

Solved! Go to Solution.

- Labels:

-

ADC

-

STM32G0 Series

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-12 09:04 PM

> it seems like using the Mcu vref+ to bias the zero on the current sense would be the best and cheapest option.

Agreed. Or use a DAC output at half scale.

> is this as simple as resistor dividing the 2.5v vref pin down to 1.65 (for 3.3v supply and symmetrical +- current) and connecting it to vref on the current sense amplifier?

Yes, if your amplifier has an offset pin, you can use a voltage divider on VREF+ to get it to half scale.

> But if I decide not to use the internal vref in the future will it be a problem that it has the divider resistance to ground connected ?

A small load on VREF+ is not a problem, whether that be internal or external. VREFBUF is specced (per the data sheet) to supply up to 4 mA. Your voltage divider should draw much less than that.

You can also choose not to load the resistors if you end up not using the voltage divider in the future. It is fairly common to add pads on the circuit board which do not get used in the final design for various reasons.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-12 09:04 PM

> it seems like using the Mcu vref+ to bias the zero on the current sense would be the best and cheapest option.

Agreed. Or use a DAC output at half scale.

> is this as simple as resistor dividing the 2.5v vref pin down to 1.65 (for 3.3v supply and symmetrical +- current) and connecting it to vref on the current sense amplifier?

Yes, if your amplifier has an offset pin, you can use a voltage divider on VREF+ to get it to half scale.

> But if I decide not to use the internal vref in the future will it be a problem that it has the divider resistance to ground connected ?

A small load on VREF+ is not a problem, whether that be internal or external. VREFBUF is specced (per the data sheet) to supply up to 4 mA. Your voltage divider should draw much less than that.

You can also choose not to load the resistors if you end up not using the voltage divider in the future. It is fairly common to add pads on the circuit board which do not get used in the final design for various reasons.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-13 07:02 AM

Thank you for the fast response.

when the vrefbuf is enabled to 2.5v and output to vref+ pin is it then also used as the reference for the ADC?

I will supply my rail to rail current sense with 3.3v same as mcu vdda/vdd. So my theoretical max output is 3.3v. Is that ok if I enable vrefbuf at 2.5? It will just saturate ADC but not damage chip?

Just Wondering if I should design my current shunt to range +- 1.25 for a 2.5 ADC reference or 1.65 for 3.3v ADC reference when using vrefbuf to generate middle sense bias.

Thanks for your help

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-13 12:35 PM

> when the vrefbuf is enabled to 2.5v and output to vref+ pin is it then also used as the reference for the ADC?

Yes.

> 1.65 for 3.3v ADC reference when using vrefbuf to generate middle sense bias.

You've just said it above: if you use VREFBUF, its voltage is ADC's reference thus 2.5V is maximum input voltage to ADC too. ADC is not referenced from VDDA pin but from VREF+ pin (to which VREFBUF is output). Only in small packages without VREF+ the reference is VDDA (as in those packages VREF+ is bonded to VDDA internally), but on those packages you must not use VREFBUF.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-13 02:23 PM

Thank you this was a very useful clarifcation.

Just one last thing to be absolutely sure - where you said " 2.5V is maximum input voltage to ADC too" - this you mean the maximum volts to avoid ADC saturation, correct? But the pin can still withstand more volts as follows from datasheet:

I am using PA0 as the ADC input (ADC_IN0).

From datasheet (STM32G071RB) this is listed as FT_a IO structure.

My VDD and VDDA is 3.3v

Under 5.2 absolute max for FT_xx is VDD+4 so 7.3

Under 5.3.1 FT_a has a max of min(vdd+3.6,5.5) so min(3.3+3.6,5.5) = 5.5

So if I design my current sensing region of interest to max out at 2.5v if a higher current happens and puts PA0 pin above 2.5v but below 5.5v the only result is ADC saturation and not chip explosion.

Thank you once again

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-13 04:16 PM

That's correct as far as I can see.

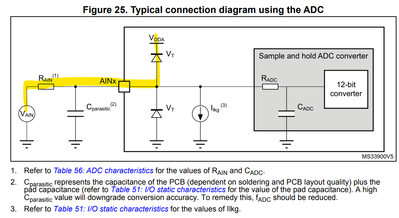

There are protection diodes in place. I suspect the following figure is simplified, but shows the general scheme.

Personally, I wouldn't want to design something with inputs above VDDA, but I can't see this concern being justified in the datasheet.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-03-14 04:25 AM - edited 2024-03-14 04:26 AM

> if a higher current happens and puts PA0 pin above 2.5v but below 5.5v the only result is ADC saturation and not chip explosion.

Most probably not, and you should stay below VDDA.

I've started a new thread to request clarification from ST for this issue. Pending relevant reply, I'd consider pins used for ADC or any other analog functionality as max.-VDDA, regardless of the fact they are FT.

But, as you've said, if the ADC input is between VREF+ and VDDA, ADC will overflow but won't explode :‑)

JW

- STM32G0 Concurrency Question in STM32 MCUs Products

- Request for Hardware design guide for STM32WL33 in STM32 MCUs Wireless

- Could not halt device (18) STM32F746G Discovery Board in STM32 MCUs TouchGFX and GUI

- Use Ethernet on nucleo STM32F767zi without RTOS in STM32 MCUs Products

- UART communication over pogopins in STM32 MCUs Products