- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- stm32f7xxx memory card - TCM.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

stm32f7xxx memory card - TCM.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-13 04:12 PM

The description of the stm32f746bg series has lines:

and L1-cache: 4KB data cache and 4KB instruction cacheSRAM: 320KB (including 64KB of data TCM RAM for critical real-time data) + 16KB of instruction TCM RAM (for critical real-time routines) + 4KB of backup SRAM (available in the lowest power modes).But there is no exact determination about possible overlapping of addresses.

The first question - L1-cache is a part of a kernel? It isn't a part available memories? I want to use 64KB+16KB of data TCM RAM without problems of the conflict with L1-cache.Second question. Address DTCM-RAM 0x20000000 + 64 Kbytes, and ITCM-RAM 0x0 + 16 Kbytes. The address space of memory from 0x20000000 turns out the linear. For an acceleration of data I just need to declare sections in duplicate: the first set of sections - fast memory, the second - a standard set of sections. If data for the first set appear less than the extent of fast memory - that the standard set will have the partial acceleration. I already checked it, works.

But there was ITCM-RAM use problem.I want to transfer the table of vectors to fast memory. Where it is possible to execute copying?Third question.

In case of switching on of the microprocessor there is the hardware reading two 32b words - 1 address of a stack (_estack), the 2nd address of function of reset (Reset_Handler). Filling of the register with the address of a stack - harmless operation. Before the first interruption it is possible to change this address as will take in head.But function of reset has unique value. I can't assign directly the address from the ITCM-RAM area, there during cold start is empty.Means to me it is necessary to execute copying of data, a program code, and the table of vectors. And after to execute change of field of loading through structure of SCB.There is a problem. How to explain to a work environment of GCC - that the residential address changes? I can execute compilation and assembly of the project with different conditions 2 times. But it is difficult and a little effective. I want that it worked.I looked for examples of use of TCM-RAM. But nothing good was succeeded to find.

I can print in Russian, so there are less losses.

#stm32f7-memory-tcm*- Labels:

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-14 12:47 PM

The question has a tag - special cruelty.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-15 01:59 AM

Hi

AVI_crak.videocrak

,About the L1 cache, I

recommend you to have a look to the

application note

I'd highly recommend you to have a look to the

application note: it provides a demonstration of the performance of the STM32F7 Series devices in various memory partitioning configurations (different code and data locations). (

-Nesrine-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-15 04:05 AM

Hi Nesrine,

Can you please push the web crew to add AN4667 you mention above to the individual 'F7xx pages? I checked only one

http://www.st.com/en/microcontrollers/stm32f746zg.html

but I could not find it there.[EDIT] it's not in the

either.Thanks,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-15 04:38 AM

Hi

Waclawek.Jan

,The

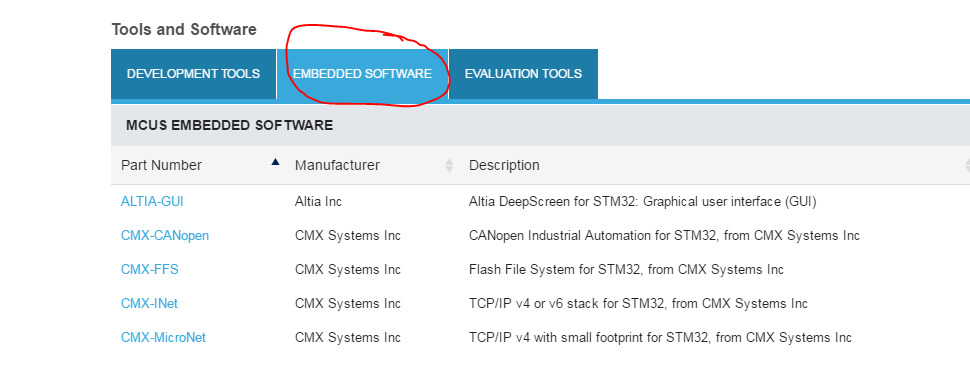

AN4667 application note is part of

software expansion for STM32Cube, so you find it under

Tools and Software > EMBEDDED SOFTWAREof

F7xx pages:

-Nesrine-

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-15 04:45 AM

Nesrine,

Yes I saw that. But that appnote contains general information pertaining to the 'F7 more than to Cube/MX, and there's a lack of such information in the appnotes offered in those places. I am not interested in Cube/MX and I am not the only one.

So, let me rephrase: please provide this or similar appnote in the basic 'F7 resources.

Thanks,

Jan

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-05-15 05:03 AM

Hi

Waclawek.Jan

I will raise your request internally for checking, and I will come back to you when I could get some updated info.

-Nesrine-

- The target device 'STM32N657Z0HxQ' is currently not supported by STM32CubeIDE in STM32CubeIDE (MCUs)

- STM32H753 SDMMC in SDIO mode producing repeated DATEND interrupt without new request in STM32 MCUs Embedded software

- sdio not working in STM32 MCUs Products

- SDIO, USB Mass Storage, and Mac in STM32 MCUs Embedded software

- SDMMC FATFS and TouchGfx Memory Issues in STM32 MCUs Embedded software