- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F745 IWDG Refresh Problem when IWDG_RLR i...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F745 IWDG Refresh Problem when IWDG_RLR is less than 4

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-07 6:50 AM

Dear All,

I am trying to use IWDG for STM32F745 and I did actually. I used CT Cube MX to configure it. Prescaler is 4, Window is 4095 and RLR is 3. I checked clock configuration and IWDG uses 32kHz RC internal oscillator and count down from RLR. I expect that when the downcounter reaches zero it will generate reset unless if IWDG doesn't refresh before it reaches zero.

32kHz with prescaler of 4, IWDG clock period is 125us.(?) If RLR is 3, I have to refresh IWDG before every 375us.

Note: I also developed code for STM32F334 and same configuration works well and I checked both user manuals are almost same. I supposed that IWDG would work easily with same configuration.

I have an ADC Interrupt Subroutine (ADC_ISR) and it hits every 40us. IWDG is refreshed inside ADC_ISR. I use one of GP Output to observe when ADC_ISR is serviced. The GPO is toggled at the beginning of ISR before refreshing IWDG. A part of ADC_ISR code is given below:

//------------------

void ADC_ISR(void)

{

HAL_GPIO_TogglePin(Diagnosis_Out_GPIO_Port,Diagnosis_Out_Pin);

__HAL_IWDG_RELOAD_COUNTER(&hiwdg); // To prevent reset caused by IWDG (Same action of HAL_IWDG_Refresh(&hiwdg);)

Counter++;

..

..

}

//----------------

When RLR is 1, 2 or 3, microcontroller resets itself even _HAL_IWDG_RELOAD_COUNTER(&hiwdg); is called every 40us. If the RLR is 4 or more than 4, microcontroller works as what it should be.

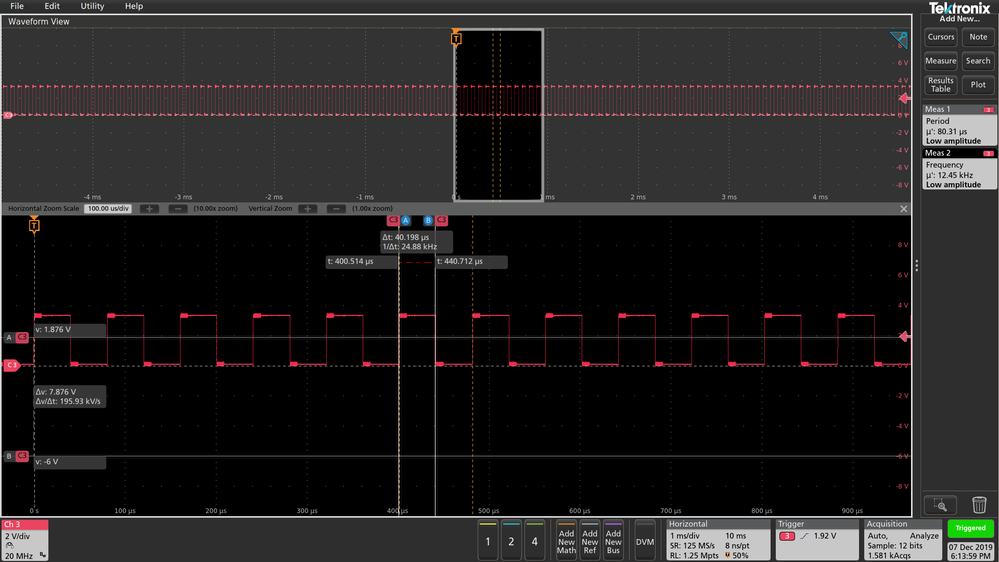

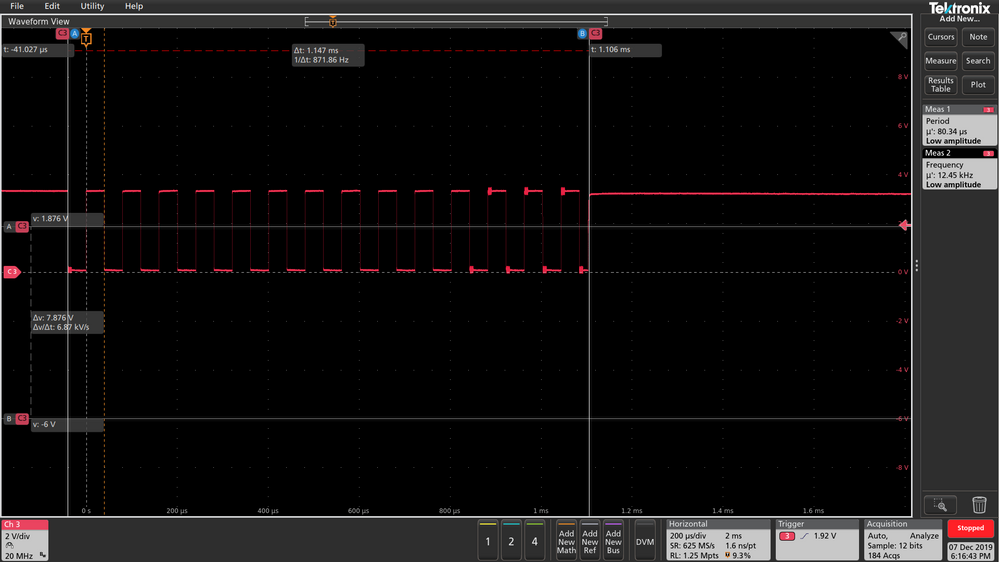

Please find scope screenshots. Figure1 shows Diagnosis output pin, it changes 30 times and after that the microcontroller resets itself where RLR is 3 and IWDG refresh is called every 40us. Figure2 is shows Diagnosis output pin again, where RLR is 4 and IWDG refresh is called every 40us. It is clear to see, if RLR is 4, microcontroller doesn’t reset itself and works as desired.

Please consult me where is the problem… For my code RLR should be 1, but I cannot set it less than 4.

Thank you very much in advance

- Labels:

-

ADC

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-07 7:29 AM

Maybe this https://community.st.com/s/feed/0D50X00009XkW4gSAF is relevant and explains your findings - I don't know as it's a different STM32 model.

JW

(This is the thread linked from there https://community.st.com/s/question/0D50X00009XkYEQSA3/iwdg-short-period-125-us-problem )

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-07 7:52 AM

A comment from ST and a remark in the reference manuals would be nice

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-08 1:06 PM

Dear Jan

I don't know what to say... It would be great if it is mentioned in the RM or the Errata Sheet... If I understand well, there is no any workarounds if we are not happy with 500us reset period...

Thank you very much

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-09 12:25 AM

Well, according to what I said there, 40us refresh should be fine with RLR=3 as it should guarantee several "kicks" out of the "guard" time of 3 LSi cycles - so either you're hit by some different issue, or the 'F745 indeed has such a "guard time" but it's longer than with the 'F4 I used.

As you've said yourself:

> I also developed code for STM32F334 and same configuration works well

ST's comment would be nice, but I wouldn't hold my breath. You may want to contact ST directly, through the web support form or through FAE.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-12-09 12:39 AM

Thank you very much. You are great... I will contact to ST... I found some other issues and I didn't send to the community becasuse I found solutions by mistake :). ST should also add the issues in the RM.

Thank you again and again

Regards

- IWDG findings in STM32 MCUs Products

- [NUCLEO-H743ZI] USB: How to check the reason of the BROKEN_PIPE(-EPIPE) message from the USB Device? in STM32 MCUs Embedded software

- SPI Global Interrupt cannot be disabled when DMA is used for SPI in Cube MX V6.5.0 in STM32 MCUs Products

- STM32F745 USB communication fails in STM32 MCUs Embedded software

- STM32F745 dual CDC problems in STM32 MCUs Embedded software