STM32F7: use of DMA to change CCR1 of timer gives transfer error

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-07 11:11 PM

Hi all,

I use DMA and linked timers in most of my projects with no problems on STM32F1 and STM32F4. I want to do the same on the STM32F7. As a test I want to use a DMA stream to create a changing signal on a PWM output. When I debug the code I see that the DMA has a transfer error but I don't understand why. Here is my initialisation code (which with some minor changes works on STM32F1): RCC_AHB1PeriphClockCmd(RCC_AHB1Periph_DMA1, ENABLE); DMA_Cmd(DMA1_Stream7, DISABLE); DMA_DeInit(DMA1_Stream7); DMA_InitStruct.DMA_Channel = DMA_Channel_3; DMA_InitStruct.DMA_PeripheralBaseAddr = (uint32_t)(&(TIM10->CCR1)); DMA_InitStruct.DMA_Memory0BaseAddr = (uint32_t)&sintab_wa; DMA_InitStruct.DMA_DIR = DMA_DIR_MemoryToPeripheral; DMA_InitStruct.DMA_BufferSize = (uint32_t)nsamp_; DMA_InitStruct.DMA_PeripheralInc = DMA_PeripheralInc_Disable; DMA_InitStruct.DMA_MemoryInc = DMA_MemoryInc_Enable; DMA_InitStruct.DMA_PeripheralDataSize = DMA_PeripheralDataSize_HalfWord; DMA_InitStruct.DMA_MemoryDataSize = DMA_MemoryDataSize_HalfWord; DMA_InitStruct.DMA_Mode = DMA_Mode_Circular; DMA_InitStruct.DMA_Priority = DMA_Priority_High; DMA_InitStruct.DMA_FIFOMode = DMA_FIFOMode_Disable; DMA_InitStruct.DMA_FIFOThreshold = DMA_FIFOThreshold_1QuarterFull; DMA_InitStruct.DMA_MemoryBurst = DMA_MemoryBurst_Single; DMA_InitStruct.DMA_PeripheralBurst = DMA_PeripheralBurst_Single; /* Wait for DMA_GetCmdStatus() */ while(DMA_GetCmdStatus(DMA1_Stream7) != DISABLE) {} /* Flush cashes to memory and wait for flush to complete */ SCB_CleanDCache(); DMA_Init(DMA1_Stream7, &DMA_InitStruct); /* Enable DMA1 channel3 */ DMA_Cmd(DMA1_Stream7, ENABLE);I have both instruction and data cache enabled, is that what's blocking? Can anyone give me some clue why I get the bus error?Thanks,Andre #stm32f7-dma-timer- Labels:

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-07 11:37 PM

Where is sintab_wa located?

Note, that in 'F7, ITCM-mapped memories (i.e. at addresses 00000000-07FFFFFF) are private to the processor and are not accessible from the bus matrix (including DMA). See AN4667 and the ARM Cortex-M7 TRM. JW- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-07 11:42 PM

Wouldn't TIM10 need to be on DMA2?

Not seeing any TIM10 trigger source in RM0410The F3 errors if trying to DMA from ROMThe F4 errors if trying to DMA from CCMConfirm memory address, and routability.Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-07 11:50 PM

sintab_wa is located in RAM (0x2001414C). I use TIM2 on DMA1 for the request (stream 7 channel 3) but I update TIM10->CCR1 with the new value from sintab_wa. Yes, I like to hookup things as much as possible :)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-08 12:11 AM

Post the relevant DMA registers' content.

JW- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-08 1:27 AM

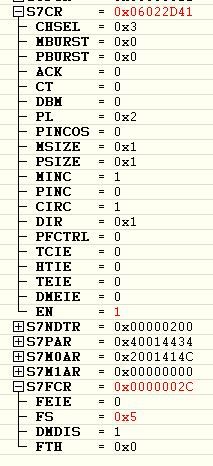

Ok, here we go:

AR.

AR.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-08 1:34 AM

I just made a small change: instead of reprogramming TIM10->CCR1 I used TIM2->CCR1. This one works... So I tried using a different timer, TIM5. This is also working. So it seems that I am not allowed to use TIM10's CCR1 as destination? Extremely strange...

AR- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-08 1:48 AM

More testing done. I have discovered that it only works with some timers:

TIM2, TIM3, TIM4, TIM5, TIM12, TIM13 and TIM14. All the other timers generate the error! I guess ST has some digging to do...AR- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2016-07-08 2:39 AM

TIM2, TIM3, TIM4, TIM5, TIM12, TIM13 and TIM14. All the other timers generate the error! I guess ST has some digging to do...

Which are all, unsurprisingly, on APB1...Up vote any posts that you find helpful, it shows what's working..