- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F410 PLL Jitter on PWM

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F410 PLL Jitter on PWM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-08-29 5:55 AM

Hello,

i want to use a really precise PWM signal but i get a lot of Jitter on it.

I am using the F410 with a 16Mhz crystal. The PLL produces from there a Frequency of 100Mhz (I need this high frequency for my other tasks).

The rest of my hardware needs one PWM signal with 1kHz and a 5ms on time. So i use a PWM Timer for that.

The problem now is, that the edges of this signal have a lot of jitter, around 3ns both on the on-time aswell on the period.

If i deactivate the PLL and directly use the 16MHz crystal for comparison, the jitter is much lower, around 0,5ns.

In the datasheed of the uC is a Table 44 about the Main PLL characteristics and in there is the Jitter with +-150ps much lower. As i see it, the chip has no option to add a external VCO-capacitor to the PLL.

Do anyone know, where this differences between datasheet and hardware come from and how can i fix this?

Best regards,

Philipp Diehl

- Labels:

-

STM32F4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-07 6:58 AM

Mhm ok so you think i should live with this?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-07 7:11 AM

Technically my "breadboard" has the same jitter as the nucleo but repeatability i switched here to the nucleo.

I have only the circuit diagram, no layout so i can`t say something about that. Do you know where i can get those?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-07 10:05 AM - edited 2023-09-07 10:14 AM

use crystal as clock - if possible (max. 50MHz using external oscillator );

if needing pll , crystal source... better not possible in this case.

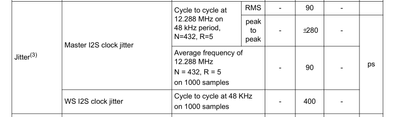

but from data -- jitter not sooo bad here , F411 :

or try other chip , i use H743 and here pll seem better...

or (as i did) with DAC, set DAC as I2S master with his own oscillator, optimum performance.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-11 9:04 AM

Hello @PDieh.1,

I propose trying these steps in your jitter measurement:

1. Configure your scope to measure all the sampled clock periods instead of just the first clock

2. Configure your scope to capture multiple periods on the screen

3. Record mean, standard deviation, and the peak to peak values

4. Repeat steps 2 and 3 25 times

Then we'll compare our results, I did those tests and the jitter looks okay (I used a scope with 50Gsa/s)

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-13 12:08 AM

I guess your oscilloscope sampling frequency from your jitter information.

because there are no another stuff on your system can be operate over 200MHz which it can be make some jitter under 5ns so your jitter less than 3ns that it may make by another stuff.

and the other condition is jitter behavior is only the edge of pulse which it can be make by 2 causes (that I known)

1. Indicator sampling - your AC Isolate, it reduce noise from other switching device on AC Line but it's no effect with own switching -> your should try to use differential probe with isolate GND between your indicator and device. I guess your will got more perspective.

2. device supply do not fast enough to recovery voltage - which this condition has 2 places first is internal regulator in stm32 and the other one is regulator supply on board.

but if this condition is root-cause, you should test by run switch many GPIO and you will see another jitter on same GPIO too because it's use same regulator.

- for this condition I think a IC buffer that support more speed than stm32 GPIO may can help to reduce this.

Lucky be with you.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-25 4:56 AM

Hello @Sarra.S ,

Sorry for the late answer, but i am not really sure what you mean with the first step.

What are all the sampled clock periods?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-10-18 1:50 AM

Hello @Sarra.S

Can you please explain, what you mean with that?

- « Previous

- Next »

- STM32F410- VCAP voltage not generated, Unable to find the target through ST-Link in STM32 MCUs Products

- Trigger ADC by TRGO in STM32 MCUs Products

- STM32U585 CLOCK JITTER in STM32 MCUs Products

- May I ask how to modify this code to replace the HAL_GPIO_EXTI_Callback () callback function? in STM32 MCUs Embedded software

- STSPIN32G4 PWM Output Jitter in STM32 MCUs Motor control