- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- STM32F4 - Timer - Max Frequency External Clock Sou...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F4 - Timer - Max Frequency External Clock Source ETR

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-30 12:51 PM

Hi,

We have a custom firmware running in an STM32F427, and I'd like to find out what the highest frequency supported on a timer with an external clock source using ETR function.

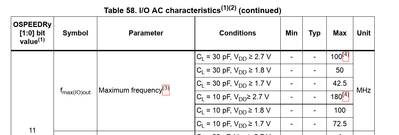

Based on AN4776, I can use a prescaler function (ETR) to read clock frequencies above the timer clock speed, due to resynchronization, I must respect a 1/3 order of the maximum APB speed. Given our APB of 90MHz, the maximum TIMClk is 30MHz.

My issue is, can I prescaler x8 this source clock and utilize it with a 240MHz clock input using the ETR function? (Timer Clock = 240/8 = 30MHz)?

Or perhaps there's something else I'm overlooking.

Solved! Go to Solution.

- Labels:

-

STM32F4 Series

-

TIM

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-03 7:08 AM - edited 2024-01-03 7:13 AM

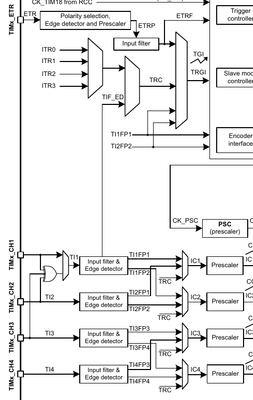

> "Timer external clockfrequency on CH1 to CH4" = 180MHz.

Right ! Input is on sync stage at first , so ...180M.

But TIM ETR input has prescaler at input - not same as CH1 to CH4 . So here and only here > 180 might be possible.

(from H563 rm)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-12-30 1:04 PM - edited 2023-12-30 1:13 PM

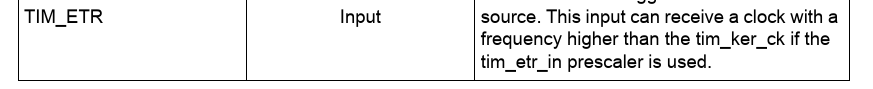

Port speed is 180MHz max. , so maybe its working at 240M - just try it. But dont rely on it - its out of spec.

+

(If i am right...) 90MHz (for timer) /4 *8 (etrp div 8 ) -> 180MHz . (same...)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-03 5:07 AM

Hi AScha.3,

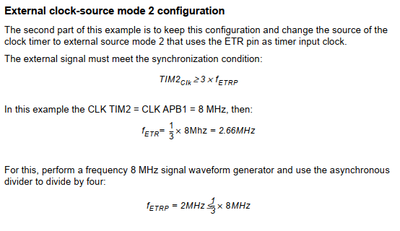

That's where I got confused because the AN4776 gives an example based on what I passed. This causes the IO to exceed the specified limits. See the example:

Even if I take the datasheet indication of 1/4 of CK_INT into account, the value reaches the maximum frequency for APB1, which is 90MHz, however APB2 is greater and may reach 180MHz. Following the same criteria as before, the maximum clock with ETR function will be 360MHz. These constraints above the IO requirements make me suspicious. What exactly am I missing?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-03 5:29 AM

I would say that the frequency must satisfy both conditions at the same time. This means, it must not exceed the IO pin limit before the divider and at the same time the frequency behind the divider must be lower then the APB sync. frequency.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-03 5:50 AM - edited 2024-01-03 5:59 AM

IMO the "digital"/"synchronous" limit should be easy to test, running the mcu at a low frequency (e.g. the default 16MHz HSI), using a waveform generator connected to ETR, and trying various ETR prescaler values.

The timer's CK_INT clock is not equal to APB clock (see RCC chapter), so I'd also try various APB prescaler values and RCC_DKCFGR.TIMPRE settings.

The table from DS talks more about ouput frequency (input should be independent from GPIOx_OSPEEDR setting, and the parameter is called fmax(IO)out). I would consider the "analog" limit to be unspecified and pending hard data from ST I wouldn't consider anything above 180MHz/2 to be reliable.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-03 6:13 AM

You missing nothing - except, any given limit in ds .

See : the PLL can run up >400MHz and so the used gates on chip should do same; as long as the input pre-divider is a simple flip-flop construct , it will do this (quite sure). Sync to core/bus is following stage, where we have to follow the recommended 1/4 of bus clock, to avoid any aliasing.

So try - it should work.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-03 6:33 AM

In datasheet table 60 is defined maximum EXT frequency "Timer external clockfrequency on CH1 to CH4" = 180MHz. It is possibly max freq. for gates and multiplexors inside MCU (for IO pins).

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-03 7:08 AM - edited 2024-01-03 7:13 AM

> "Timer external clockfrequency on CH1 to CH4" = 180MHz.

Right ! Input is on sync stage at first , so ...180M.

But TIM ETR input has prescaler at input - not same as CH1 to CH4 . So here and only here > 180 might be possible.

(from H563 rm)

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2024-01-03 8:26 AM

Hello, AScha.3.

This was my first understanding of the ETR function, but given the limits mentioned on the datasheet and the lack of additional information, I was uncomfortable advancing with experiments without a third opinion from you experts. My first thought was something along the lines of Mr. Waclawerk.Jan said.

I'll run some tests and see how the SI behaves in the 100MHz to 240MHz range in practice.

To clarify our scenario, we are using this as an input syncronyze for an external DAC's clock, and our goal is to reach a higher frequency in order to reduce spurs and phase noise in the system.

Thank you for all of your comments and answers!

- Debug STLink GDB Server v.1.3.0 - PARSE ERROR: Argument: -cp in STM32CubeIDE for Visual Studio Code (MCUs)

- STM32U535 LPBAM LPTIM3 capture problem in STM32 MCUs Embedded software

- STM32F4 I2C CR2 Peripheral clock frequency in STM32 MCUs Products

- STM32G4: Using PC13 for calibrating RTC – how bad can it be, really? in STM32 MCUs Products

- STM32H755ZI custom board not detected by ST-Link in STM32 MCUs Products