- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM32F4 DMA Request Mapping Table & TIM1/TIM8 ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM32F4 DMA Request Mapping Table & TIM1/TIM8 confusion

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-09 03:58 PM

Using the STM32F446RE with very good results so far including ADC1,ADC2,ADC3 DMA to SRAM arrays. ADCs and DMA (peripheral to memory) were fairly easy but the TIMER 1 and TIMER 8 PWM usage is giving me some problems in understanding how DMA and the Advanced timers work. I may have to move one or two of my ADC DMA Streams/Channels but that's OK as long as the other choices will allow what I need.

I have been working on getting tables periodically loaded into two (2) TIM1 and TIM8 Capture Compare Registers (CCR1 & CCR2 or CCR3)) using DMA . Four (4) output pins from each timer for each corner of a full wave bridge circuit. Negated and Non-Negated CCR PWM outputs are working good (also Dead Time) using a fixed timer interrupt to stuff the waveform table values into the CCRs but this really needs to be done from DMA waveform tables and triggered using ITR0-ITR4 methods using Timer 2, 3, 4 or 5.

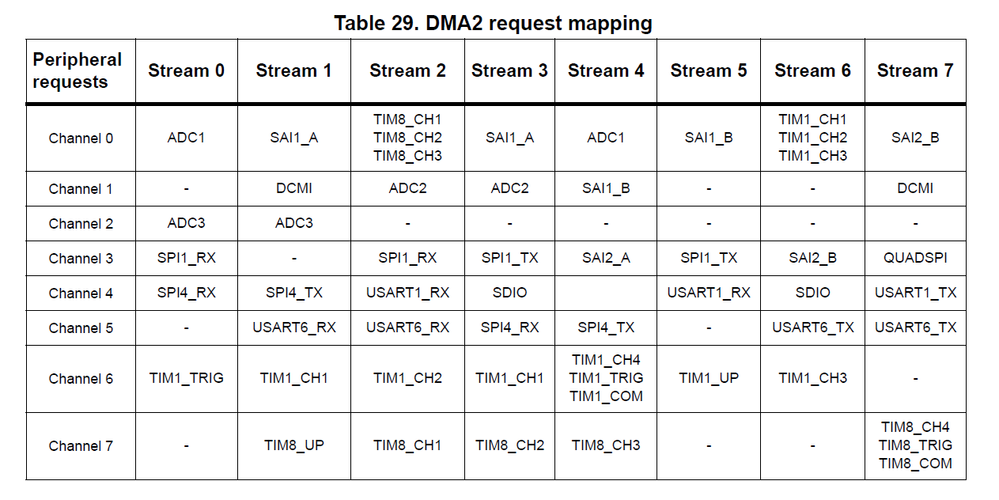

But I am confused with some of the terms used in the DMA2 mapping table. I have searched quite a bit and found hints in example code and documentation but am now needing to post questions because nobody, it would appear, is doing what I am trying to do. I am attaching a pic of the DMA2 table here for quick reference.

Stream 2 Channel 0 shows three Timer 8 CCRs I'm pretty sure....

TIM8_CH1

TIM8_CH2

TIM8_CH3

Same with Stream 6 Channel 0 for TIMER 1 and CH1, CH2, CH3.

Which one(s) is it ? Is it all three at the same time with one waveform indexed table value or can CH1 be updated with the first waveform table's indexed value, CH2 with the next value and CH3 with the 3rd table value or are they all the same value being sent to all 3 Channels ?

To be useful for 3 phase PWM, I believe all 3 channels would need to be updated with a different value from a different table (different source addresses) or one waveform table with interleaved values, 1,2,3,1,2,3,1,2,3 etc. There is only one source address so it must be interleaved I am guessing. Memory to Peripheral of course.

The Advanced Timer chapters don't seem to address this in a way I can understand either.

Then there is Stream 4, Channel 6 showing 3 different uses...

TIM1_CH4

TIM1_TRIG

TIM1_COM

What and/or how are these 3 used ? TIM1_CH4 is most likely CCR4, Not exactly sure about TIM1_TRIG (must be Timer 1 Trigger but how ?), and I do not find much about what exactly TIM1_COM means. Is it COM for COMmunications ? COMMUTATE ?

Same thing for Stream 7 Channel 7 for TIM8.

One more... Stream 1 Channel 7 is TIM8_UP and Stream5 Channel 6 TIM1_UP....

Is this UP for UPDATE ? UP for UP count ? Can't exactly tell. One sentence on these would most likely clear up my confusion on these terms.

Any and all help with describing these or pointing to some documentation or better examples are MUCH appreciated !

Thank you SO much !

boB

- Labels:

-

DMA

-

STM32F4 Series

-

TIM

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-09 05:37 PM

UP is for UPDATE / ZERO COUNT

Where there are multiple sources, you can usually select which at the TIM

There is a TIM specific address/mapping for writing multiple registers in a burst. My understanding is you could have 3 values in the array for each trigger, and you'd be able to update all three CCR at CH1, CH2 and CH3 fire point. For one rotation the array would contain 9 values.

Not a mode I use, but basically some I think could be validated with some minimal effort.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-05-10 03:06 PM

Thank you Clive !

I was thinking that too for the 3-phase CCR update. Will continue with software and see if it is the way we think it might work.

As for the TIMx_UP in the DMA table, the reference manual talks about "updates" of course in the timer chapters BUT the only actual reference I see for this, having to do with interrupts.....

Position Priority Type Acronym

25 32 settable TIM1_UP_TIM10 TIM1

OK, found a list of defines that give me a bit of information on the TIM1_UP and TIM1_TRIG (+TIM8) confusion...

#define TIM_DMA_UPDATE (TIM_DIER_UDE)

#define TIM_DMA_CC1 (TIM_DIER_CC1DE)

#define TIM_DMA_CC2 (TIM_DIER_CC2DE)

#define TIM_DMA_CC3 (TIM_DIER_CC3DE)

#define TIM_DMA_CC4 (TIM_DIER_CC4DE)

#define TIM_DMA_COM (TIM_DIER_COMDE)

#define TIM_DMA_TRIGGER (TIM_DIER_TDE)

Now I have some register field bits to refer to that refer back to those individual terms in the table.

boB