- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: STM spi master sending extra clock signals.

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

STM spi master sending extra clock signals.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-23 05:44 AM

I am trying to communicate with an adc chip acting as a spi slave to my stm32f3 spi master. So far I am unable to make it work.

After attaching an oscillscope I found out that if i send only 8 bits of data to the slave , I get exactly 16 clock pulses on the SCLK of my master even though I have set the data size as 8.

My master config is

SPIx->CR1 |= SPI_CR1_SSI;

SPIx->CR1 |= SPI_CR1_SSM;

SPIx->CR1 |= SPI_CR1_BR_0 | SPI_CR1_BR_2;

SPIx->CR1 |= SPI_CR1_MSTR;

SPIx->CR1 |= SPI_CR1_CPOL;

SPIx->CR1 |= SPI_CR1_CPHA;

SPIx->CR1 |= SPI_CR2_DS_0 | SPI_CR2_DS_1 | SPI_CR2_DS_2;

SPIx->CR1 &= ~SPI_CR1_RXONLY;

SPIx->CR1 |= SPI_CR1_SPE;

SPIx->CR2 |= SPI_CR2_FRXTH;I write 8 bits simply as

while (!(SPIx->SR & SPI_SR_TXE));

SPIx->DR = 0x54;

while (!(SPIx->SR & SPI_SR_RXNE));

while (SPIx->SR & SPI_SR_BSY);I am NOT sending any dummy bytes from the master to read back from slave. Right now I just want to send 8 bits to slave and see 8 clock pulses.

Can someone tell me what might be going on here?

- Labels:

-

ADC

-

SPI

-

STM32F3 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-23 07:21 AM

Ok so I found out that I had to access the DR in 8bit mode. That solved the extra clock cycles issue. Now I see another issue.

SCLK is not idling high even though I have set CPOL=1.

If I run a simple program from mbed and run on the hardware it is able to talk to the slave ADC just fine. The only difference between my implementation and the mbed program seems to be the clock.

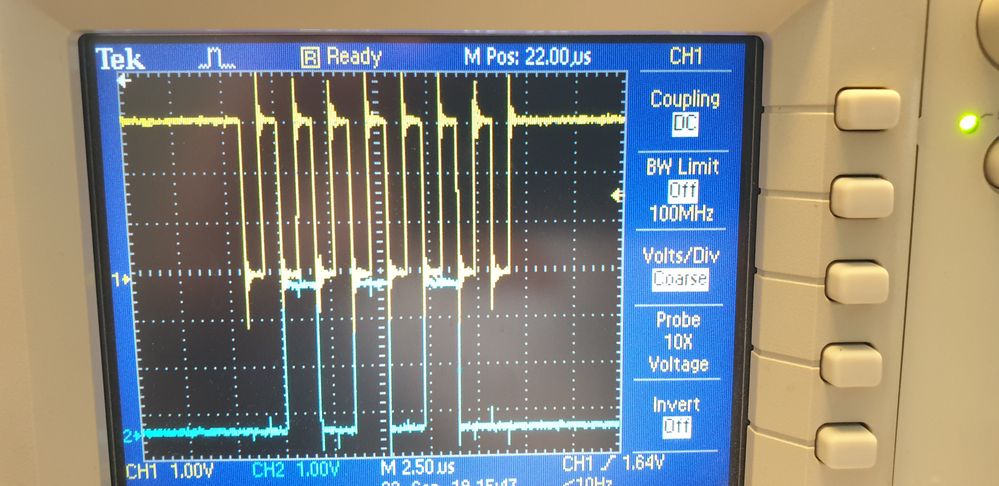

Following is from my mbed program which is able to send command to adc and read back the reg. (sending 0x54=0b01010100 cmd)

Yellow is SPI clk, blue is MOSI

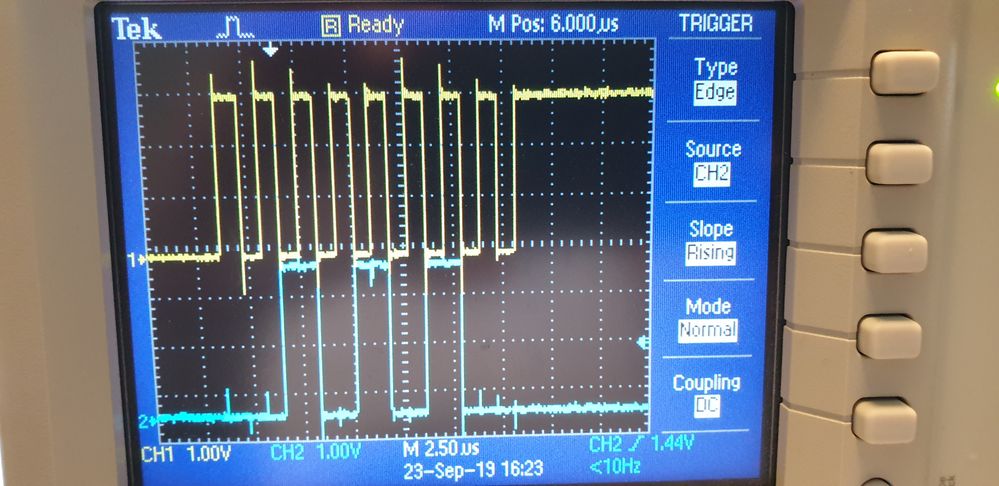

Pic below is from my own lowlevel SPI implementation

Yellow is SPI clk, blue is MOSI

The master clk in second pic is not idling high. Can this explain why I am unable to talk to the slave using my SPI config?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-23 07:51 AM

So basically in the second case I was sending the SPI msg from master immediately after enabling SPI. After adding artificial delay , now both mbed and my implementation CLK/MOSI signals look the same.

Still no answer from the slave spi (works with mbed program). Now I am at a total loss. any one got any ideas?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-23 08:20 AM

Do you use NSS signal with your ADC?

What is the ADC part number?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-23 08:48 AM

I have configured a GPIO pin as slave select and I do a manual SET/RESET on this pin. The ADC is Analog Devices 7913

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-23 09:02 AM

I moved the HAL_GPIO_WritePin line just before my write_cmd and now it seems the slave chip is responding fine.

HAL_GPIO_WritePin(SPI_CS_GPIO_Port, SPI_CS_Pin, GPIO_PIN_RESET);

write_cmd(LOCK_KEY_READ);

recv_reg = write_cmd(0x00);Previously I was setting the pin low even before enabling the SPI module.

Does it matter how long before the CS was made low?(in my scenario CS low activates the slave)

Edit: In the ADC timing diagram I didn't find any constraint that CS has to be active just before transmission. Is this normal behaviour?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-09-23 10:22 AM

When a slave is not selected (CS high), usually its MOSI/MISO pins are high impedence (not listening to the bus).

- ADC measuring only high side of Centered Mode PWM (HRTIM) in STM32 MCUs Products

- STM32 U545 - ADC DMA in STM32 MCUs Products

- HRTIM PWM transients greater than a period in STM32 MCUs Products

- PC13 GPIO Usage recommendation on STM32G491MCT in STM32 MCUs Products

- synching HRTIM's TIMA and TIMB in STM32 MCUs Products