- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: Setting the USART baud-rate

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Setting the USART baud-rate

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 9:06 AM

Hi Everyone,

We have managed to increase the clock speed for STM32F722 using PLL. Now we are wondering how we can keep the baud rate of USART6 to 115200 bit/s (is there any function/capability in STM32F722 that automatically adjusts the USART clock divider and set the baud rate after changing the Micro's clock speed or no?)

Your quick response is highly appreciated.

Thanks,

Dan

- Labels:

-

STM32F7 Series

-

UART-USART

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 12:52 PM

Generally the quickest way to adjust is to flip the UE (UART Enable) bit, write the new BRR that accounts for the shift in clocking rate, and then renable the UE bit.

I think the H7 provides for alternate clocking sources, ie not just APB, but don't think the F722 has that.

You could also play with the APB dividers separately from the PLL, to keep the buses at a more consistent speed, but the ratio there are somewhat limited. Careful selection of speeds would permit easier transitions.

When changing clocks there is potential for data loss in any active RX/TX operation.

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 1:12 PM

USART peripherals (and some others too) use 2 different clocks, so called kernel clock and interface clock. Interface clock is the one used to access to registers on APB bus while kernel clock is the one generating baudrate.

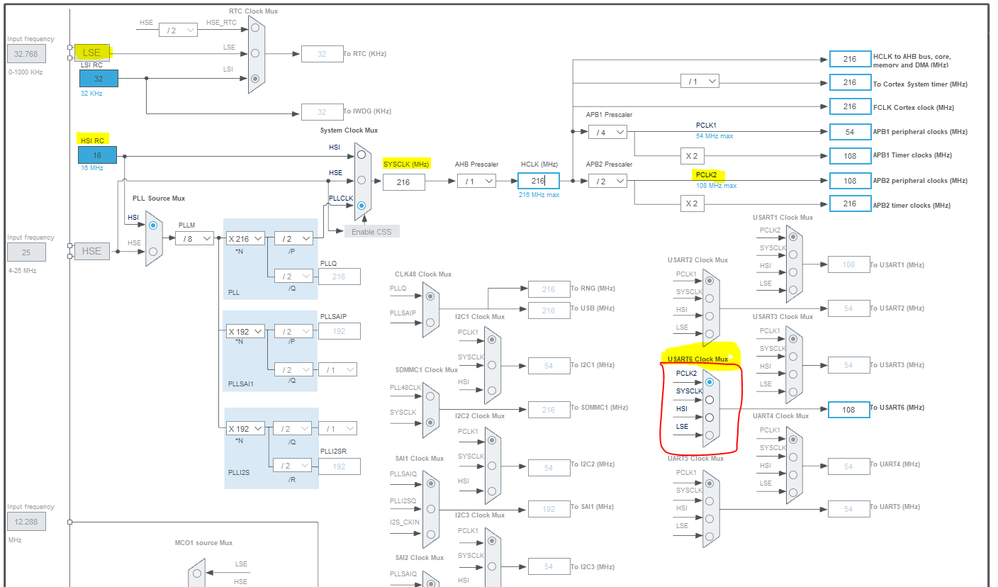

Specifically for USART6 you can pick one of these clocks: PCLK2, SYSCLK, HSI, LSE. First one is by default and is derived from system clock. If you modify system clock (as you did by modifying PLL), then you modify PCLK2 too. Same goes for SYSCLK. But you can use HSI, High Speed Internal, or Low-Speed-External LSE clock.

Here I would then suggest you to use HSI, 16MHz in this case. You set baudrate BRR register according to your needs and then you can modify interface clock (with PLL) without stopping UART and enabling it back. Effectively you are safe from data loss.

See image below. You can modify kernel clock for USART with RCC registers.

Tilen

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 1:49 PM

Hi Tilen,

Unfortunately, I can't use cubeMX program to set USART6 baud-rate. I need to set that in the program. So I was wondering where in the code I can change the mentioned clock sources? and which part of the codes are used to set the USART6 baud-rate?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 2:04 PM

You don't need CubeMX to use it, I just took an example to show you how are clocks related.

You did not tell us what drivers you use, but anyway, as said before, RCC block is the one you need to focus to configure any clock, including kernel clocks for IP.

Register DCKCFGR2 in RCC.

Please note that HSI might not be the best source for driving UART baudrate. Please check datasheet for max and min values for HSI oscillator. Best would be to disable UE bit, modify BRR and re-enable UE bit for USART instead.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 9:27 PM

Thanks Tilen for your useful explanation. We could figure out how to change the clock source for USART based on your explanation. Now we need to know how baud rate can be set and which registers and/or functions should be used for this purpose?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-06 10:19 PM

As CliveOne pointed out, you need to write new value to BRR register of USART peripherals. We do not know which drivers (libraries) you use but in case of LL, there is a function called LL_USART_SetBaudrate which does it for you. Do not forget to disable USART first.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-08 7:28 AM

Hi Tilen,

Thanks a lot for your help.

We managed to change the baud-rate and the core clock frequency. Our goal is to read one of the ports at the highest frequency (108 MHz) and send its data to the serial port. However, at higher core frequencies (more than 40 MHz), STM32F722 seems to hang/become unstable and the serial communication will be lost. I need to add that We currently use an external 12MHz crystal as an input for the PLL which is used for generating clock for the STM32F722. Do you know what may lead to this problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-08 7:28 AM

Hi Tilen,

Thanks a lot for your help.

We managed to change the baud-rate and the core clock frequency. Our goal is to read one of the ports at the highest frequency (108 MHz) and send its data to the serial port. However, at higher core frequencies (more than 40 MHz), STM32F722 seems to hang/become unstable and the serial communication will be lost. I need to add that We currently use an external 12MHz crystal as an input for the PLL which is used for generating clock for the STM32F722. Do you know what may lead to this problem?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2019-08-08 7:34 AM

You'd need to make sure the USART isn't mid transaction when you change baud rate, or data loss will occur. Also the RX will stop if it flags framing or noise errors, you'll need to clear those.

12 MHz clock will be fine, generally these devices support crystals in the 4-25 MHz range, and oscillators up to 50 MHz or more.

Up vote any posts that you find helpful, it shows what's working..

- STM32H563 USART clock behaviour between HSI and HSE in STM32 MCUs Boards and hardware tools

- STM32H7S3L8 LL DMA USART TX transfer in STM32 MCUs Products

- STM32WB05KN co-processor USART is not responding (bluetooth) in STM32 MCUs Wireless

- FDCAN1 error in STM32G431 with interrupt vectors. in STM32 MCUs Embedded software

- Automatic USART Baudrate detection for STM32H523 in STM32CubeMX (MCUs)