Sampling difference between ADC3 and 4 in STM32G474 - Error in ADC4??

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-19 12:39 AM

Dear ST-community,

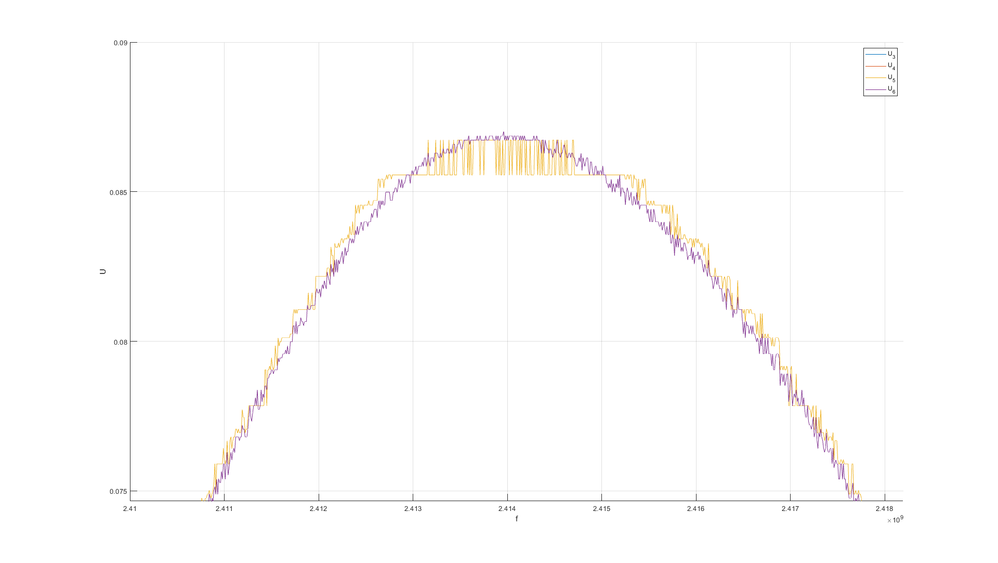

I am trying to sample four basebandvoltages simultaneously. Therefor, I trigger 4 ADCs with the same timer in dual simultaneous mode. However, I encountered a problem with the digitized voltages. An image is attached (Y: ADC3, P:ADC4). ADC 3 and 4 are sampling the same voltage. However, as you can see, the digitized values are different. I already changed the MCU and the channels (switched from slow to fast channel), but the problem stayed the same. The same thing arises with ADC1 and 2 where 2 is the one with the problem. Is such a behaviour known and what can be done about that?

Thank you a lot in advance.

Best regards

Ben

- Labels:

-

ADC

-

STM32G4 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-19 4:25 AM

Does increasing of sampling time of ADC4 (or both ADCs) make any difference?

You also might want to read the 'G4 ADC appnote.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-19 4:33 AM

Hi Jan,

thanks for your answer. Well increasing the sampling time reduces noise. However, the jumps at certain voltages remain. I also calibrate the ADCs now at startup, which I think, made a little improvement.

Best regards

Ben

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-19 5:48 AM

Inadequate VREF decoupling?

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-19 6:22 AM

actually I use the ones proposed in the datasheet & as close as possible at the pins. This would also affect the other ADCs wouldn't it?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-20 8:14 AM

Hard to tell. It's not as "digital" as you'd think. The particular routing inside the package (and on the chip itself) matters.

Have you read AN5346 and the errata? Besides decoutpling VREF, I think the main recommendation from there is to decrease the ADC frequency; but it's worth a thorough reading IMO.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2020-06-20 8:47 AM