M7 with 4xRAM ICs over FMC

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-09-25 5:13 AM - edited 2023-09-26 11:18 PM

Hi,

We have a question about a system design we would like to implement for our product.

We are working with the STMF32F723 MCU and are developing our own HW. We need 216MByte of RAM for our application and would like to implement it with the functionality of DMA and FMC.

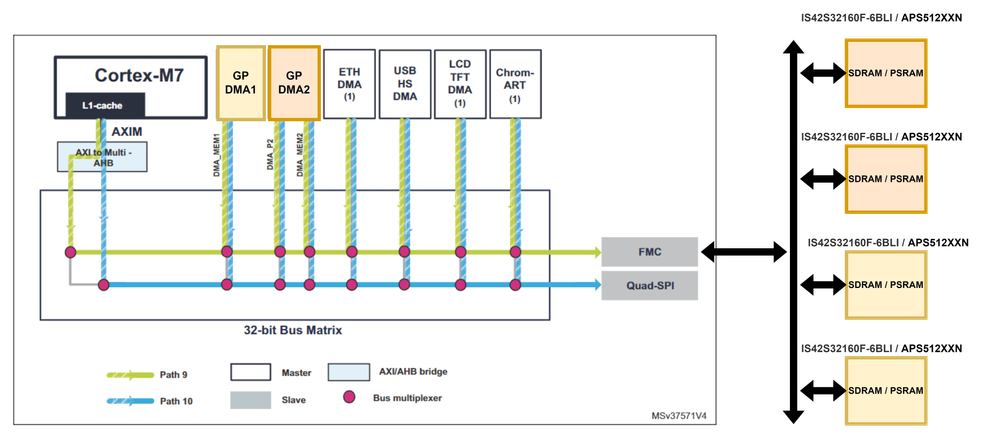

Here is a figure which shows the system architecture with the help of the graphic from application note AN4667.

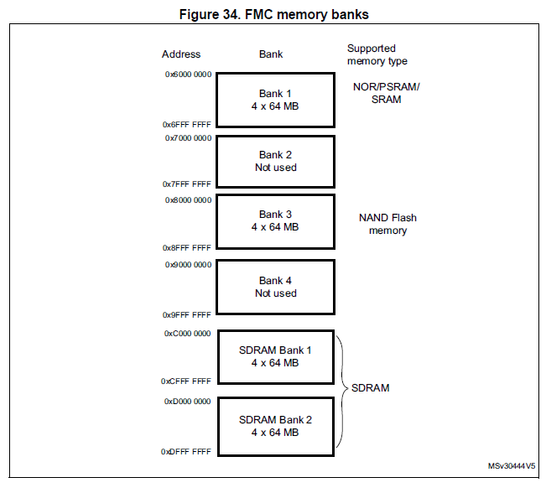

From the reference manual RM0431, we found following FMC memory bank map:

Now the question are:

- Is this system architecture possible at all?

- Could we use 4 blocks(64MByte) of PSRAM or also 4 Blocks(64MByte) of SDRAM?

- What are the benfits of SDRAM over PSRAM (which one is better for what?)

- Does it make sense, that two memory blocks are controlled over DM1 and the other two over DM2?

- So we can Read from one of the first two with DM1 and at the same time write to one of the oder two with DM2?

- What constraints do we need to consider when choosing the right RAM ic?

- Would the IS42S32160F-6BLI (SDRAM) or APS512XXN (PSRAM) both fit to the FMC of the M7 MCU?

Best regards,

Corsin

- Labels:

-

DMA

-

FMC-FSMC

-

RAM

-

STM32F7 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-16 6:02 AM

Fyi, for QSPI RAM, Memory Mapped read should be no issue, but Memory Mapped Write is not supported on this MCU

Alex

- « Previous

-

- 1

- 2

- Next »