- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Re: low latency signal generation using timer and ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

low latency signal generation using timer and DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-30 12:20 PM

Hey everyone,

I used a one pulse mode master signal that triggers a slave timer. The slave timer then generates a one pulse waveform with repetition counter set to 5.

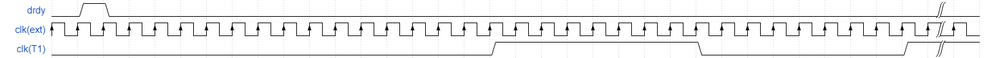

I want to generate the signal above, It receives a pulse called drdy and is fed by an external clock at a frequency of 24 MHz. After the DRDY pulse it should remain low for 16 rising edges of the external clock, then it should toggle a pin 12 times, each toggle after 8 clock pulses,after which it should stop till the next drdy pulse.

The latency on just using the timer to generate this is too long, I'd need the rise time and reaction of the signal to be sub 20 ns. Could I implement a DMA with the timer to generate this for very low latency?

Thanks in advance for any help!

#dma-normal #waveform-generator #aribtary-waveform #software-timer- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-30 02:27 PM

I used a one pulse mode master signal that triggers a slave timer. The slave timer then generates a one pulse waveform with repetition counter set to 5.

How is it relevant to the given problem?

The latency on just using the timer to generate this is too long

Latency between what and what, and in which timer of which STM32? Describe, how would you intend to implement it. Draw diagrams.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-30 05:04 PM

Hi

Waclawek.Jan

,I used a one pulse mode master signal that triggers a slave timer. The slave timer then generates a one pulse waveform with repetition counter set to 5.

How is it relevant to the given problem?

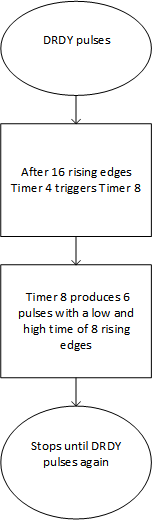

This was what i used to generate the waveform above and sort of how I approached the problem.

When drdy went high It would trigger a timer which would remain low for 16 edges and then go high. Once it goes high it triggers a secondary timer in one pulse mode, It outputs a pulse with length 8 and period Which then repeats itself 6 times and the stops(using the repetition counter). The waveform came out correctly but was extremely low latency between periods where the counter would reach overflow and the transition of the gpio pin.

Here's a picture of the whole waveform(it repeats itself every time DRDY pulses):

How is it relevant to the given problem?

How is it relevant to the given problem? The latency on just using the timer to generate this is too long

Latency between what and what, and in which timer of which STM32? Describe, how would you intend to implement it. Draw diagrams.

JW

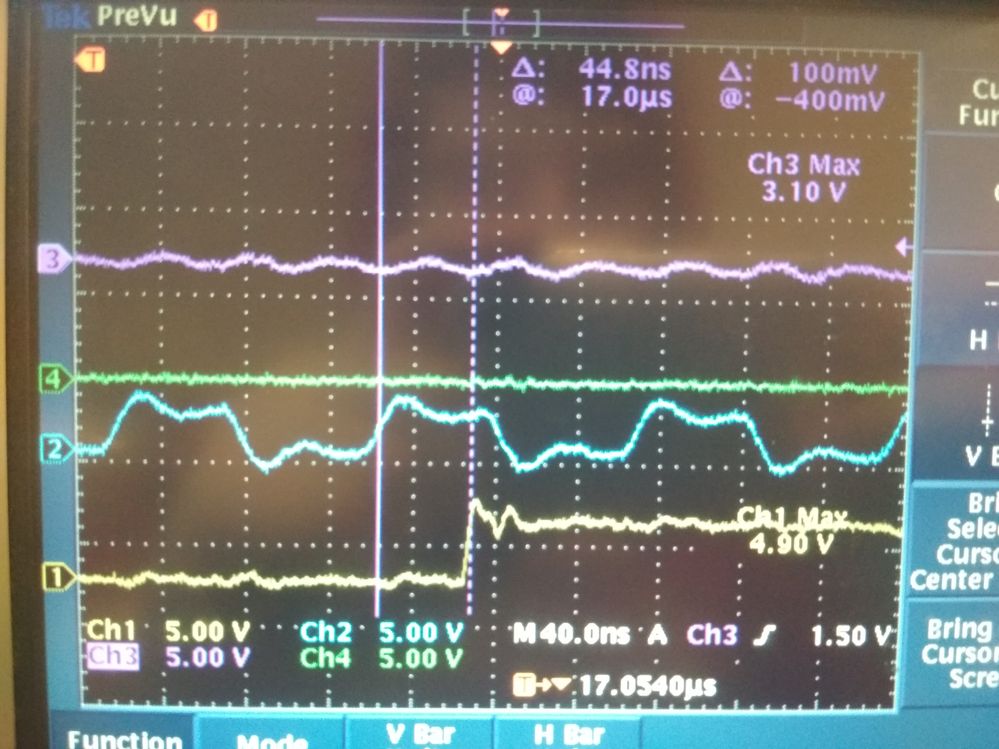

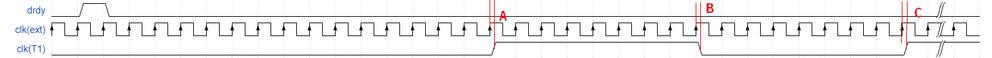

The latency is between the external clock that is going into ETR2 of Timer 8(which produces the 6 pulses) and 4(which triggers timer 8) on the stm32f722ze and its output when it reaches overflow. At merely 8 MHZ, it provides a latency of nearly half a clock cycle to transition.Shown below is a external clock frequency of 8MHz, at overflow it takes 44 nanoseconds to transition to a high state on timer8. This is with fast mode enabled and pins set to very high frequency

If I could at all generate a waveform that stays low for 16 rising edges of the external clock after the drdy pulse and then transitions on every 8 clock pulses of the external clock to generate 6 pulses with low latency between when overflow occurs and the pin is toggled I would be very happy.

Sorry if there is still any ambiguity, please let me know

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-30 05:47 PM

So is the problem the delay at A, at B, at C, at all of them, or something else?

I suspect all of them, correct?

I am not very familiar with exact timing between ETR and the clock advancement; and between the compare event and output; and AFAIK this is not documented well if at all. There is certainly at least one synchronizer (i.e. delay between one to two timer clock, depending on the particular phase between external signal's edge and timer clock's edge) at the ETR input, and I suspect there may be at least one more between the compare unit and the output. Start with a simple few-clock PWM driven from the external clock, and measure the latency, varying the timer clock (i.e. related APB clock, through the APB divider, or for that matter changing the system clock, whatever you find easier).

You may be better off deliberately delaying the whole pulse train by a whole external clock cycle, by setting a filter on ETR. That again is driven from the respective APB clock.

IMO DMA won't help you here: the input signal is again through timer i.e. at least the input portion of delay is still there; and the arbitration within the DMA and on the buses involves not only delay but also jitter (i.e. that delay is varying, depending on what does the rest of the system do).

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-04-30 06:15 PM

Hi

Waclawek.Jan

,Thank you for the help,

It would be the latency at all of them.

So I should generate a PWM signal and measure the latency between it and the external clock to double check?

Could you please elaborate on the following:

You may be better off deliberately delaying the whole pulse train by a whole external clock cycle, by setting a filter on ETR. That again is driven from the respective APB clock.

Would there be any other way to generate this waveform that would allow less latency?

Thank you for all the help thus far

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-01 02:47 AM

So I should generate a PWM signal and measure the latency between it and the external clock to double check?

Yes. And assess the impact of timer clock=APB frequency on it.

I'd also say, that ETR is sampled by the DTS clock, so changing TIMx_CR1.CKD will probably also have some impact.

Could you please elaborate on the following:

You may be better off deliberately delaying the whole pulse train by a whole external clock cycle, by setting a filter on ETR. That again is driven from the respective APB clock.

If it turns out that the delays between input signal at ETR and output are prohibitively long, you may increase that delay deliberately, by switching on the ETR filtering (in TIMx_SMCR.ETF), so, that that delay gets slightly longer than one full external clock cycle. Then, by decreasing the number of external clock cycles used to delay the first edge, you'll achieve the waveform you wanted. This of course works only if the external clock is known to have a stable frequency.

A variant on this 'trick' is to delay the output by one external clock cycle using an external edge-triggered latch (e.g. a 74xx74); relaxing to great extent the requirement for known clock frequency.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-29 01:27 PM

Hi

Waclawek.Jan

,I think I might have been misunderstanding something and there could be an easier solution to what I'm doing.

I was using the above signal to trigger another timer which then triggers a DMA to move data from the gpio pins to ram. For some reason I thought only having a timer in input capture could trigger the DMA in this way.

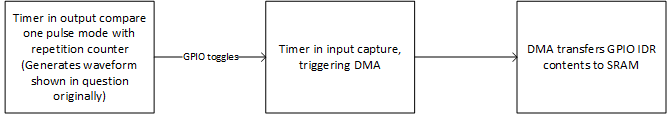

So essentially this:

One timer(on the left) which generates a control signal for when the secondary timer should trigger the DMA to move the contents from the GPIO IDR to SRAM.

Secondly what I'm thinking is the reaction time is slow(relatively) not due to the timers but rather toggling of the GPIO pin in the waveform above.

What I'm proposing is to have the same signal generated by the first timer but not output it via gpio, rather have the counter be incremented with a repetition counter and at every point where overflow occurs the DMA is triggered directly.

This seems like a much better solution than chaining timers by gpio that I was originally doing and should result in a very fast response? I'm thinking sub 20 ns as its all hardware?

I just want to check my logic with you.

Thanks for all the help thus far.

I really appreciate all your input

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-29 04:05 PM

Sure any intermediate step increases delays, but I still don't quite understand what are you trying to accomplish, sorry.

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2018-05-30 03:04 AM

There's a Cube software package and relevant Application Note that perhaps could help you in this:

- How to configure GPDMA for PWM generation? in STM32 MCUs Products

- PWM help in STM32 MCUs Products

- TIM_OCActive example, setting TIM1 CH1 output pin PA8 to HI is visible for all four channels in STM32 MCUs Products

- STMCubeIDE won't include SPI HAL driver in STM32CubeIDE (MCUs)

- Bug in TIM_Base_SetConfig, fix TIM_Base_SetConfig to block first interrupt in STM32 MCUs Embedded software