- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- Jitter between ADC1 and ADC2 in ADC + DMA

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

Jitter between ADC1 and ADC2 in ADC + DMA

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-22 2:06 AM

First of all: I am aware of

https://community.st.com/t5/stm32-mcus-products/jitter-in-adc-dma-mode/m-p/231446#M51827

but cannot see how the accepted answer solves the (my?) issue.

Setup description:

I use

- STM32H723VGHx

- ADC1 and ADC2 are setup in

- Dual regular simultaneous mode

- DMA access mode

- delay between 2 sampling phases 1.5 cycles

ADC1:

ADC2:

If required, I could provide additional info about timer setups, etc.

In my code, I react to the ADC Conversion Complete Callback:

void HAL_ADC_ConvCpltCallback(ADC_HandleTypeDef* hadc) {

if (hadc->Instance == ADC1) {

stopMeasurement();

}

}

where stopMeasurement basically stops the configured TIM3, stops the DMA and restarts the DMA for the next cycle.

Tim3 is then restarted later on by another timer.

Problem description:

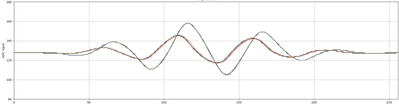

The expected data are two sine waves shifted by a certain (fixed phase):

I captured these waves with an alpha setting for plotting (with some window applied):

(please check in full screen).

The ADC1 is in "blueish" color, ADC2 in "reddish"

What I observe is that the ADC2 data is "jumping" from a "prominent" picture to the same picture shifted one data point to the right. Statistically this happens quite rarely but often enough to be problematic (maybe 5% of the data points)

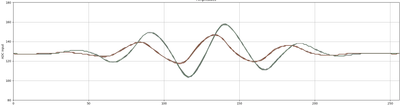

Almost solution

I changed the configuration of ADC1 to use 2.5 cycles in ADC_Regular_ConversionMode.Rank.SamplingTime, leaving the ADC2 configuration untouched. By doing so, I can reduce the statistical occurrence of these "jumps" to <1% of data captures. However they are not completely gone.

Possible explanation (?)

With the initial setup the syncing of ADC1 and ADC2 is not perfect. As ADC1 conversion complete callback is basically stopping the data capture, in statistically some cases, the adc conversion is not completed when the callback occurs and the adc2 data point is for some reason written to the first register of the next iteration. By extending the sampling time of adc1 I achieve that adc1 finishes "more often" its work after adc2 and therefore the "race condition" issue does not happen (or at least less often)

Quesitons:

- Is my possible explanation correct?

- Is there a more elegant way to solve my issue?

- Labels:

-

ADC

-

DMA

-

STM32H7 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-22 6:56 AM

You should be able to run ADC1 and ADC2 in dual mode, in which case they will sample at the exact same time.

As for your particular problem, I suspect there's a program logic error somewhere, perhaps DMA is stopped before ADC, so a spare sample remains and gets sent when resumed again. You could consider using circular mode without stopping it. Or reset the state of the DMA and ADC prior to the start of each measurement.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2023-11-23 7:25 AM

Hello @AndreasInhofer

You need to take care to configure properly the duration of the master and slave conversions so that a DMA request is generated and served for reading both data (master + slave) before a new conversion is started.

Did you check ADSTP command of ADC_CR of the master ADC?

Note that master and slave should be configured with the same sampling time. Also, you need to program the same number of conversions in the master’s sequence as in the slave’s sequence. Otherwise, the remaining conversions will not generate a DMA request.

To give better visibility on the answered topics, please click on Accept as Solution on the reply which solved your issue or answered your question.

Best regards,

FBL

- HSO on G431 in STM32 MCUs Motor control

- G071 LPTIM encoder mode creeps around in STM32 MCUs Products

- ADC DMA Multiple channel in STM32 MCUs Embedded software

- STM32G431RB — ADC1 Interrupt and ADC2 DMA (7 Channels) with FreeRTOS — External Voltage Detection in STM32 MCUs Embedded software

- "No proper path for Current Sensing" error despite connectAlgo.log finding TripleADC route on STM32G474 in STM32 MCUs Motor control