- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- IWDG disable during Sleep/Stop

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

IWDG disable during Sleep/Stop

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-05 1:57 PM

Hello.

I am running STM32L412 microcontroller in low power GSM design. All works great, but I would also want to add watchdog just in case.

I am in STOP2 mode most of the time, and I am waiting for interrupts from GSM module or MEMS IRQ

I configured IWDG for 30s reset, I reload it just before sleep that takes 4 minutes (IWDG = 30s).

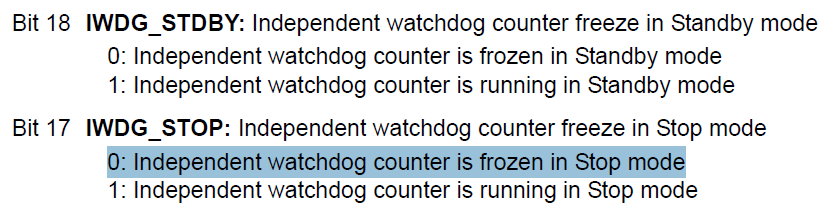

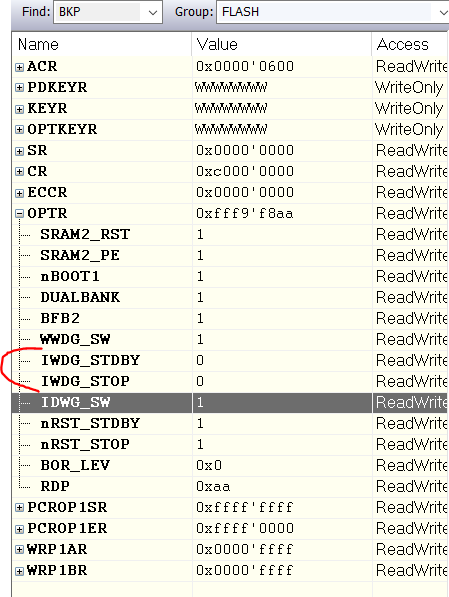

In boot I also RESET IWDG_STOP and IWDG_STBY bits based on reference manual, I also check FLASH OP register to see if bits are truly zeros and they are.

Any ideas what I am doing wrong ?

FLASH_UNLOCK();

FLASH_OB_UNLOCK();

CLEAR_BIT(FLASH->OPTR,FLASH_OPTR_IWDG_STOP|FLASH_OPTR_IWDG_STDBY);

FLASH_OB_LOCK();

FLASH_LOCK();

void FLASH_UNLOCK(void)

{

if(READ_BIT(FLASH->CR, FLASH_CR_LOCK) != 0U)

{

FLASH->KEYR = FLASH_KEY1;

FLASH->KEYR = FLASH_KEY2;

if(READ_BIT(FLASH->CR, FLASH_CR_LOCK) != 0U)

{

//return 1;// ERROR

}

}

}

void FLASH_OB_UNLOCK(void)

{

if(READ_BIT(FLASH->CR, FLASH_CR_OPTLOCK) != 0U)

{

FLASH->OPTKEYR = FLASH_OPTKEY1;

FLASH->OPTKEYR = FLASH_OPTKEY2;

}

else

{

//return 1;// ERROR

}

//return 0;

}- Labels:

-

IWDG-WWDG

-

Power

-

STM32L4 series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-05 2:20 PM

Read about the FLASH_OPTR functionality and programming in the reference manual.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-05 2:36 PM

Could you be more specific whats wrong ? OPTR resgisters are protected at boot and cleared, be me afterwards, but IWDG still resets MCU in STOP2 mode.

What do I am missing or do not understand, clearing FLASH_OPTR_IWDG_STOP should stop IWDG running while in STOP2 mode, and prevent it from reset, right ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-05 3:21 PM

You are missing the part where you are reading the reference manual section about option byte programming! Or just opening the link I gave and looking at an absolutely specific code example in the accepted answer... What's so hard in these actions?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-06 12:06 AM

Hello. Again, I think I don't have problem with FLASH option bytes writing, since i already have implemented EPROM emulation on internal flash ,

I don't have any hard faults or resets because of it ( I had when starting IWDG programing, but it was because i was not unlocking flash register)

And I have correct data after programing in option register and my program runs like it should.

Your answer to me looks like RTFM, so if you know WHY IWDG IS NOT FROZEN IN STOP2 and still manages to generate reset ( yes, I check, reset source was IWDG and not hard fault or anything like that), I would would be extreamly happy if you can point me to something precise like missing bit or not enabled something.

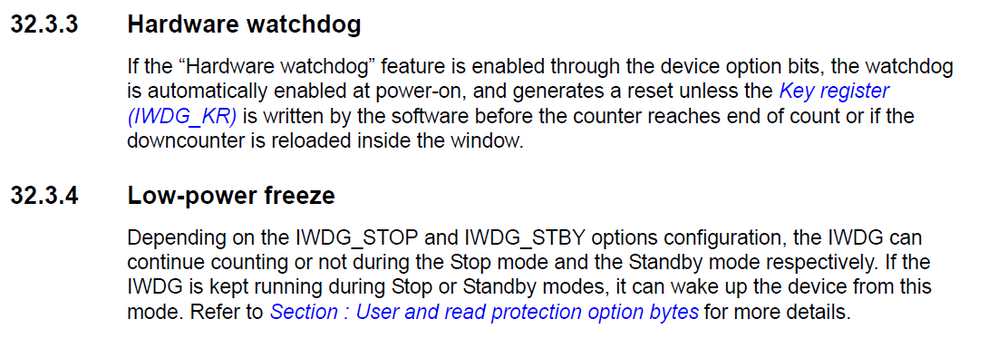

I have 4 minutes LPTIM1 controlled sleep, and IWDG max time is 30s, so if my program is running, it does it because i am keep reloading IWDG, and when I go to STOP2, after 30s my program was reseted, and I need to prevent it !

Since it is impossible to disable IWDG once enabled....

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-06 1:20 AM

Looks like I get it working. Problem was I was not clearing IWDG_SW (to enable Hardware independent watchdog) bit.

And it's very hard to understand why I need to do this, since reference manual does not give simple answer.

And yes, Piranha, your code did that, but I was not clear why. RM is not that clear I needed to do it in low power freze...

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-06 12:33 PM

No, EEPROM emulation has nothing to do with option bytes. And no, IWDG_SW has nothing to do with stopping IWDG in low-power modes.

The RM0394 Rev 4 section "3.4.2 Option bytes programming" explains all of this very clearly. But you don't understand it because you haven't done the RTFM. When you will read it, you will also understand what and why my code does.

P.S. The current "best answer" doesn't actually answer anything and is just wrong on IWDG_SW.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-06 9:52 PM

So can you explain why my code runs now the way I expected ?

update:

Ok, so I looks like I am missing OPTSTRT and OBL_LAUNCH procedure, and IWDG just gets updated registers after reset.

I will add this to my code. I gess I so hang up on seeing that registers are updated, just did not understand/read that they need to be launched to take effect.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2022-11-08 4:14 PM

See, reading the reference manual helps and my first post was spot on! ;) Good that now you will understand that register and what the code does.

- STM32G491 FDCAN2 Receiving Issue in STM32 MCUs Products

- STM32G0B1RE + CAN-FD 4 (NCV7344) - CAN FD frames not reaching receiver Raspberry Pi (MCP2517FD) in STM32 MCUs Products

- nucleo-c092rc CANFD 8Mbits not working in STM32 MCUs Products

- Unable to activate SAI on stm32h7s78-dk in STM32 MCUs Embedded software

- CubeMX STM32WB55 linker file problem? in STM32CubeMX (MCUs)