- STMicroelectronics Community

- STM32 MCUs

- STM32 MCUs Products

- In what order are registers pushed into the stack ...

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

In what order are registers pushed into the stack after the exception occurs?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-21 10:24 AM

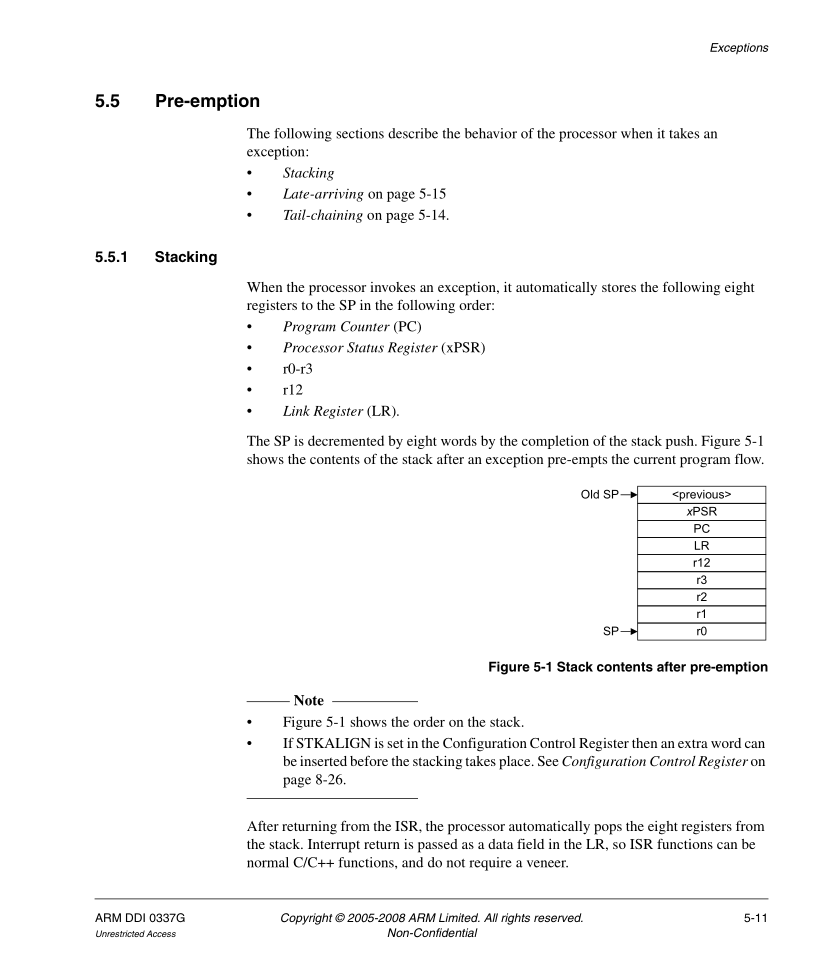

In Cortex M3, what is the order in which the register are pushed into the stack?

Which of the following orders are correct (if any)?

First Order:

PC

PSRx

R3

R2

R1

R0

R12

Link Register

Second Order:

PC

PSRx

R0

R1

R2

R3

R12

Link Register

Please Guide? Thanks in advance?

#cortex-m3 #stm32f103rb #exception #arm- Labels:

-

STM32F1 Series

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-21 10:34 AM

JW

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-21 12:03 PM

Where

R0 = [SP + 0]

R1 = [SP + 4]

etc

Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-21 12:12 PM

void hard_fault_handler_c(unsigned int * hardfault_args, unsigned int r4, unsigned int r5, unsigned int r6)

{ printf ('\n[Hard Fault]\n'); // After Joseph Yiuprintf ('r0 = %08X, r1 = %08X, r2 = %08X, r3 = %08X\n',

hardfault_args[0], hardfault_args[1], hardfault_args[2], hardfault_args[3]); printf ('r4 = %08X, r5 = %08X, r6 = %08X, sp = %08X\n', r4, r5, r6, (unsigned int)&hardfault_args[8]); printf ('r12= %08X, lr = %08X, pc = %08X, psr= %08X\n', hardfault_args[4], hardfault_args[5], hardfault_args[6], hardfault_args[7]);printf ('bfar=%08X, cfsr=%08X, hfsr=%08X, dfsr=%08X, afsr=%08X\n',

*((volatile unsigned int *)(0xE000ED38)), *((volatile unsigned int *)(0xE000ED28)), *((volatile unsigned int *)(0xE000ED2C)), *((volatile unsigned int *)(0xE000ED30)), *((volatile unsigned int *)(0xE000ED3C)) );while(1);

}Up vote any posts that you find helpful, it shows what's working..

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Email to a Friend

- Report Inappropriate Content

2017-11-21 12:13 PM

See how it indexes hardfault_args here, we pass in SP as parameter ♯ 1, ie R0

Up vote any posts that you find helpful, it shows what's working..

- Issue with custom Bootloader in STM32 MCUs Products

- How to use STLINK-V3 + remote OpenOCD to debug? in STM32CubeIDE (MCUs)

- STM32L031 RTC Wake up interrupt service routine never entered in STM32 MCUs Embedded software

- Regarding the cause of HardFault_Handler in STM32 MCUs Products

- STM32F756 jumps unknown address "BX LR" in STM32 MCUs Products